下载

PLASTIC

DUAL-IN-LINE

(NT)

PLASTIC

CHIP CARRIER

(FN)

CERAMIC WINDOWED

DUAL-IN-LINE

(JTL)

TICPAL22V10Z-25C, TICPAL22V10Z-30I

EPIC™ CMOS PROGRAMMABLE ARRAY LOGIC CIRCUITS

SRPS007D − D3323, SEPTEMBER 1989 − REVISED DECEMBER 2010

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Copyright © 2010, Texas Instruments Incorporated

1

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

• 24-Pin Advanced CMOS PLD

• Virtually Zero Standby Power

• Propagation Delay Time:

I, I/O to I/O in the Turbo Mode

-25C . . . 25 ns Max

-30I . . . 30 ns Max

I, I/O to I/O in the Zero-Power Mode

-25C . . . 35 ns Max

-30I . . . 40 ns Max

CLK to Q

-25C . . . 15 ns Max

-30I . . . 20 ns Max

• Variable Product Term Distribution Allows

More Complex Functions to Be

Implemented

• Each Output Is User-Programmable for

Registered or Combinatorial Operation,

Polarity, and Output Enable Control

• Extra Terms Provide Logical Synchronous

Set and Asynchronous Reset Capability

• Preload Capability on All Registered

Outputs Allow for Improved Device Testing

• UV Light Erasable Cell Technology Allows

for:

Reconfigurable Logic

Reprogrammable Cells

Full Factory Testing for High

Programming Yield

• Programmable Design Security Bit

Prevents Copying of Logic Stored in Device

• Package Options Include Plastic

Dual-In-Line and Clip Carrier [for

One-Time-Programmable (OTP) Devices]

and Ceramic Dual-In-Line Windowed

Package

.

AVAILABLE OPTIONS

PACKAGE TYPE

T

A

RANGE

0°C to 75°C TICPAL22V10Z-25CJTL TICPAL22V10Z-25CNT TICPAL22V10Z-25CFN

−40°C to 85°C NA TICPAL22V10Z-30INT TICPAL22V10Z-30IFN

EPIC is a trademark of Texas Instruments Incorporated.

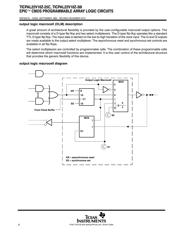

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

CLK/I

I

I

I

I

I

I

I

I

I

I

GND

V

CC

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I

JTL AND NT PACKAGE

(TOP VIEW)

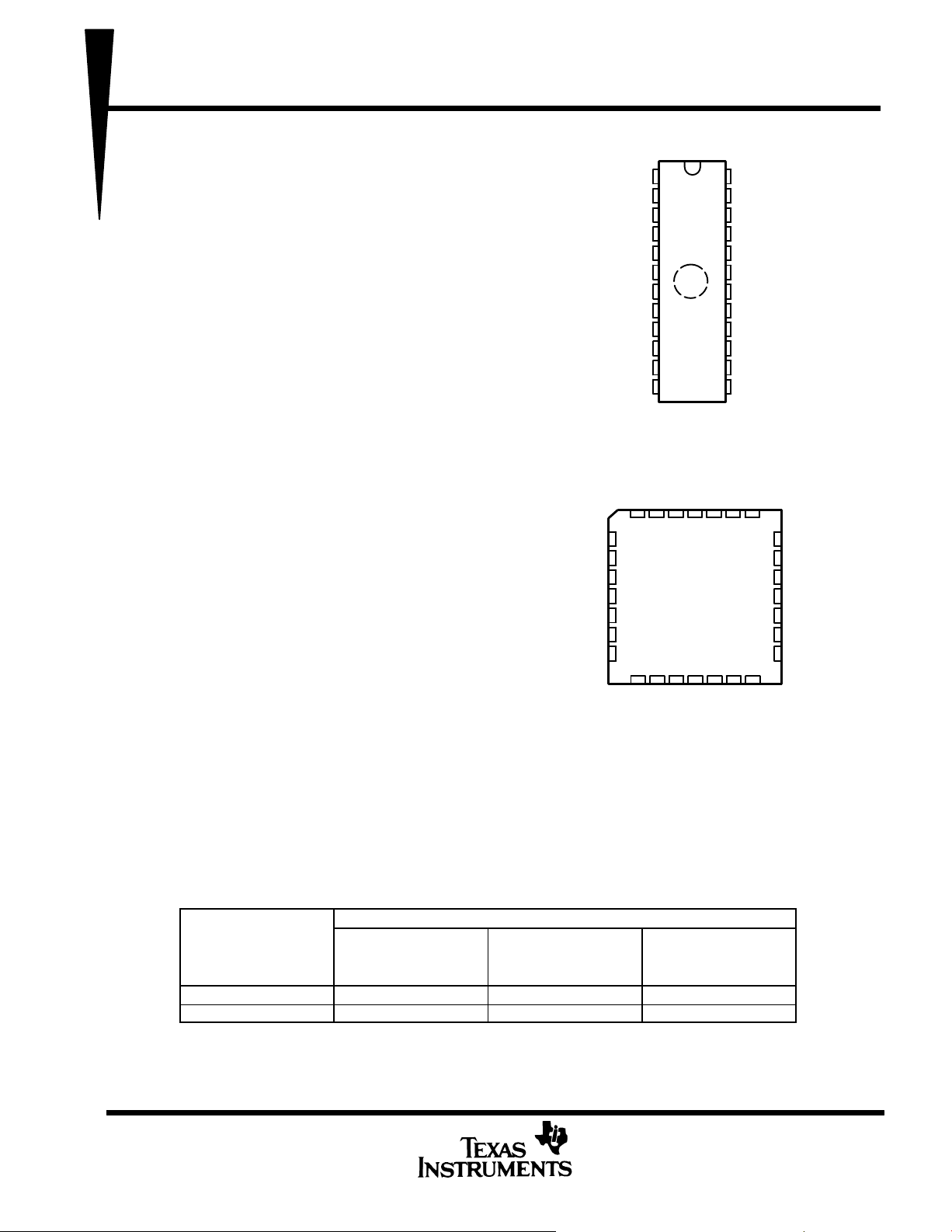

3212827

12 13

5

6

7

8

9

10

11

25

24

23

22

21

20

19

I/O/Q

I/O/Q

I/O/Q

NC

I/O/Q

I/O/Q

I/O/Q

I

I

I

NC

I

I

I

426

14 15 16 17 18

I

I

GND

NC

I

I/O/Q

I/O/Q

I

I

CLK/I

NC

I/O/Q

I/O/Q

FN PACKAGE

(TOP VIEW)

NC

− No internal connection

Pin assignments in operating mode

V

CC