下载

200-MHz Field Programmable Zero Delay Buffe

r

CY23FP12

Cypress Semiconductor Corporation • 3901 North First Street • San Jose, CA 95134 • 408-943-2600

Document #: 38-07246 Rev. *E Revised December 13, 2004

Features

• Fully field-programmable

— Input and output dividers

— Inverting/noninverting outputs

— Phase-locked loop (PLL) or fanout buffer configu-

ration

• 10-MHz to 200-MHz operating range

• Split 2.5V or 3.3V outputs

• Two LVCMOS reference inputs

• Twelve low-skew outputs

— 35ps typ. output-to-output skew (same freq)

• 110 ps typ. cycle-cycle jitter (same freq)

• Three-stateable outputs

•< 50-µA shutdown current

•Spread Aware

• 28-pin SSOP

• 3.3V operation

• Industrial temperature available

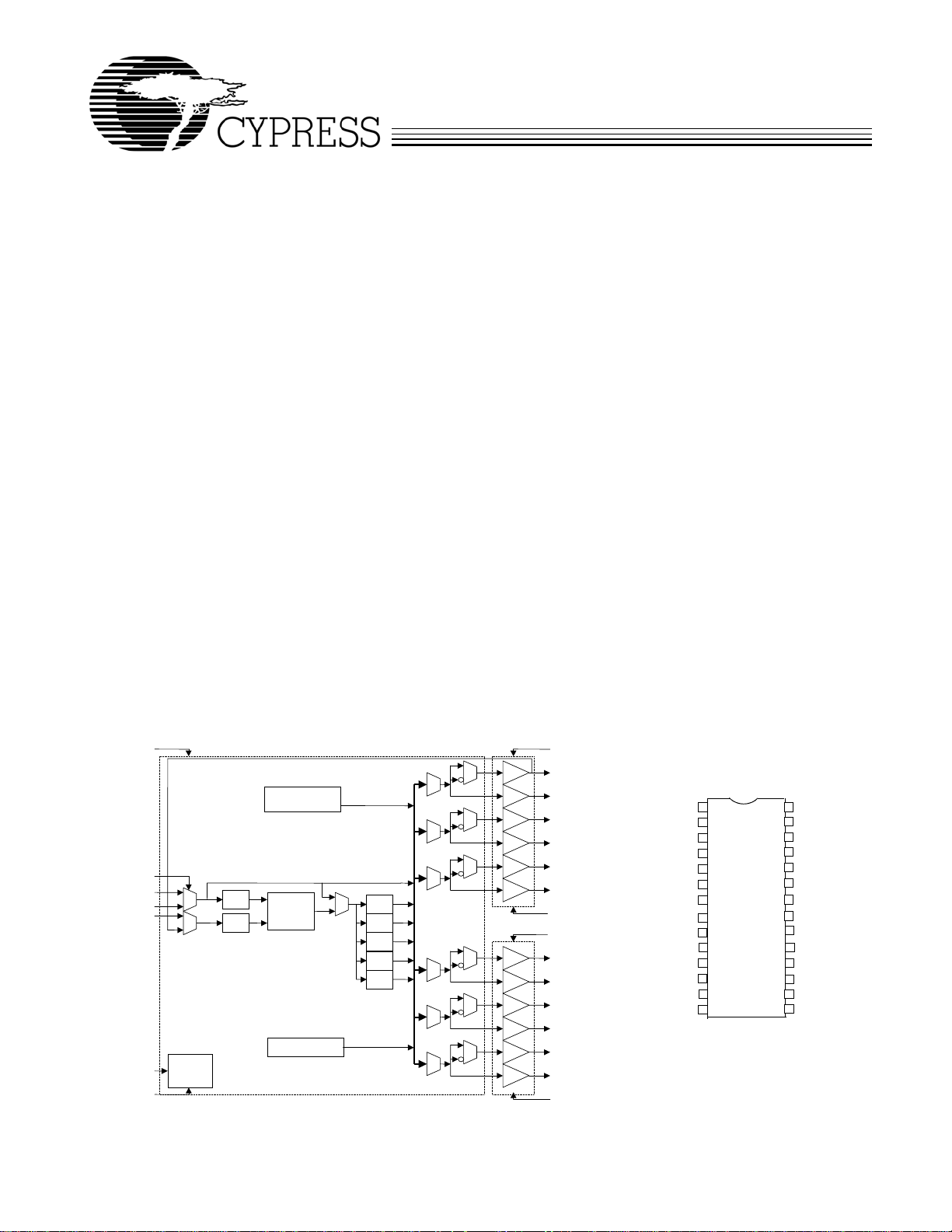

Functional Description

The CY23FP12 is a high-performance fully field-program-

mable 200 MHz zero delay buffer designed for high speed

clock distribution. The integrated PLL is designed for low jitter

and optimized for noise rejection. These parameters are

critical for reference clock distribution in systems using

high-performance ASICs and microprocessors.

The CY23FP12 is fully programmable via volume or prototype

programmers enabling the user to define an appli-

cation-specific Zero Delay Buffer with customized input and

output dividers, feedback topology (internal/external), output

inversions, and output drive strengths. For additional flexibility,

the user can mix and match multiple functions, listed in

Table 2, and assign a particular function set to any one of the

four possible S1-S2 control bit combinations. This feature

allows for the implementation of four distinct personalities,

selectable with S1-S2 bits, on a single programmed silicon.

The CY23FP12 also features a proprietary auto-power-down

circuit that shuts down the device in case of a REF failure,

resulting in less than 50 µA of current draw.

The CY23FP12 provides twelve outputs grouped in two banks

with separate power supply pins which can be connected

independently to either a 2.5V or a 3.3V rail.

Selectable reference input is a fault tolerance feature which

allows for glitch-free switch over to secondary clock source

when REFSEL is asserted/deasserted.

21

28

REFSEL

FBK

CLKA0

CLKA1

V

SSA

CLKA2

CLKA3

V

DDA

1

2

3

4

5

6

7

8

22

23

24

25

26

27

REF2

REF1

CLKB0

CLKB1

V

SSB

CLKB2

CLKB3

V

DDB

SSOP

Top View

Pin Configuration

17

V

DDA

20

V

SSA

19

CLKA4

18

CLKA5

16

V

SSC

15

S1

9

V

SSB

12

V

DDB

13

V

DDC

10

CLKB4

11

CLKB5

14

S2

FBK

÷

M

÷

N

100 to

400MHz

PLL

CLKA1

CLKA3

CLKA2

REF2

REFSEL

CLKA4

CLKA5

CLKB1

CLKB3

CLKB2

CLKB4

CLKB5

VDDA

VSSA

VDDB

V

SS

B

÷

2

÷

3

÷

4

÷

X

CLKA0

VDDC

VSSC

÷

1

Lock Detect

Test Logic

REF1

CLKB0

S

[

2:1

]

Function

Selection

Block Diagram

[+] Feedback