下载

1

Copyright

Cirrus Logic, Inc. 2000

(All Rights Reserved)

P.O. Box 17847, Austin, Texas 78760

(512) 445 7222 FAX: (512) 445 7581

http://www.cirrus.com

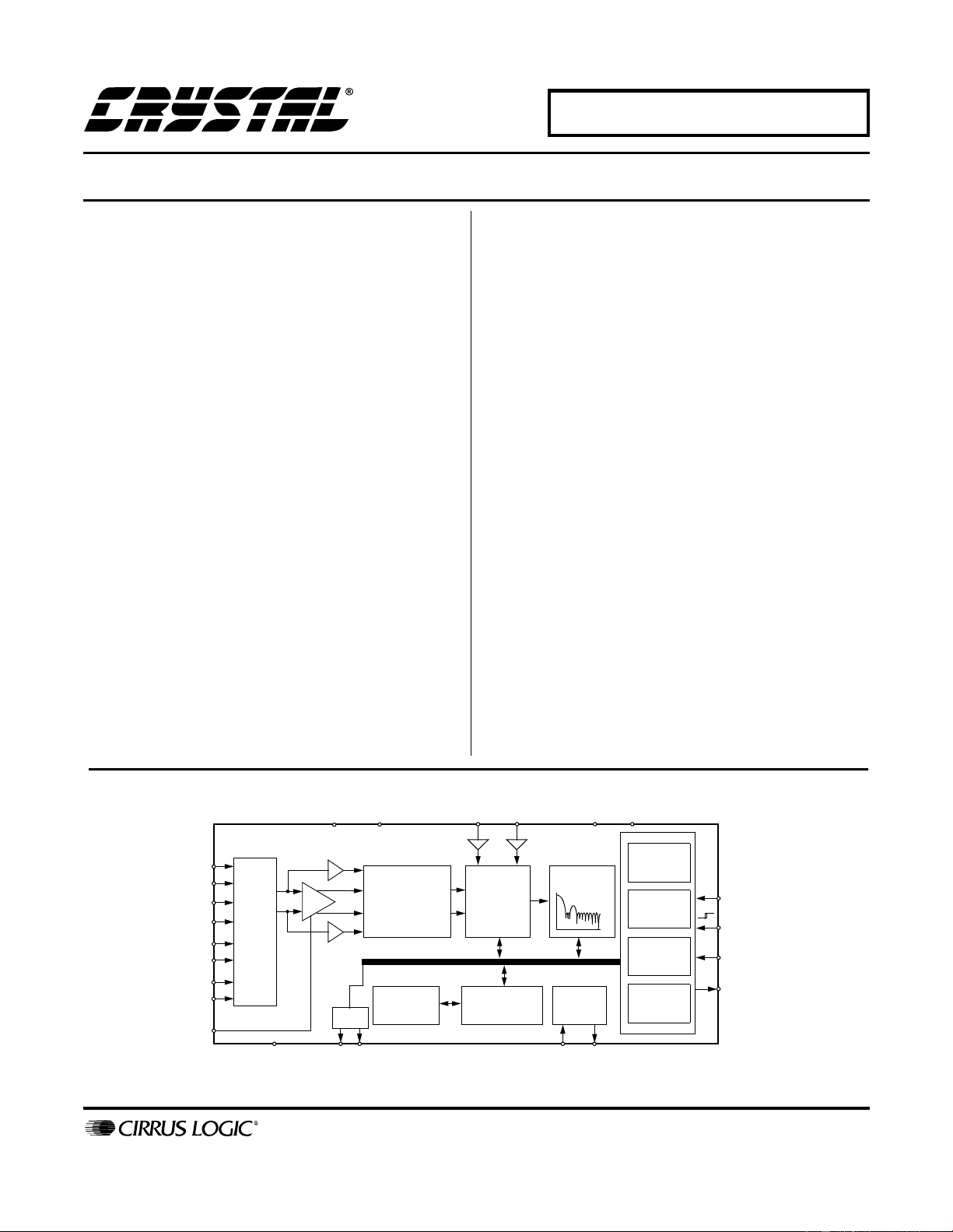

CS5521/22/23/24/28

16-Bit or 24-Bit, 2/4/8-Channel ADCs with PGIA

Features

l Low Input Current (100 pA), Chopper

Stabilized Instrumentation Amplifier

l Scalable Input Span (Bipolar/Unipolar)

- 2.5V VREF: 25 mV, 55 mV, 100 mV, 1 V, 2.5 V,

5V

- External: 10 V, 100 V

l Wide V

REF

Input Range (+1 to +5 V)

l Fourth Order Delta-Sigma A/D Converter

l Easy to Use Three-wire Serial Interface Port

- Programmable/Auto Channel Sequencer with

Conversion Data FIFO

- Accessible Calibration Registers per Channel

- Compatible with SPI

TM

and Microwire

TM

l System and Self-Calibration

l Eight Selectable Word Rates

- Up to 617 Hz (XIN = 200 kHz)

- Single Conversion Settling

- 50/60 Hz ±3 Hz Simultaneous Rejection

l Single +5 V Power Supply Operation

- Charge Pump Drive for Negative Supply

- +3 to +5 V Digital Supply Operation

l Low Power Consumption: 5.5 mW

General Description

The CS5521/22/23/24/28 are highly integrated ∆Σ Ana-

log-to-Digital Converters (ADCs) which use charge-

balance techniques to achieve 16-bit (CS5521/23) and

24-bit (CS5522/24/28) performance. The ADCs

come as

either two-channel (CS5521/22), four-channel

(CS5523/24), or eight-channel (CS5528) devices, and

include a low input current, chopper-stabilized instru-

mentation amplifier. To permit selectable input spans of

25 mV, 55 mV, 100 mV, 1 V, 2.5 V, and 5 V, the ADCs

include a PGA (programmable gain amplifier). To ac-

commodate ground-based thermocouple applications,

the devices include a Charge Pump Drive which pro-

vides a negative bias voltage to the on-chip amplifiers.

These devices also include a fourth order ∆Σ modulator

followed by a digital filter

which provides eight selectable

output word rates

. The digital filters are designed to settle

to full accuracy within one conversion cycle and when

operated at word rates below 30 Hz, they reject both 50

and 60 Hz interference.

These single supply products are ideal solutions for

measuring isolated and non-isolated, low-level signals in

process control applications.

ORDERING INFORMATION

See page 51.

Programmable

Gain

VA+ AGND VREF+ VREF- VD+DGND

XIN XOUT

SDO

SDI

NBV

Latch

Differential

Digital Filter

Calibration

Register

Control

Register

Output

Register

4th Order

∆Σ

Modulator

Calibration

Memory

Calibration

µ

C

Clock

Gen.

SCLK

CS

MUX

AIN2+

+

X20

X1

X1

X1

CS5524

Shown

AIN2-

AIN1+

AIN1-

AIN4+

AIN4-

AIN3+

AIN3-

A0 A1

CPD

Data

FIFO

MAY ‘00

DS317F2