下载

DS123 (v2.19) June 6, 2016 www.xilinx.com

Product Specification 1

© Copyright 2003–2016 Xilinx, Inc. XILINX, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Xilinx

in the United States and other countries. All other trademarks are the property of their respective owners.

Features

• In-System Programmable PROMs for Configuration of

Xilinx® FPGAs

• Low-Power Advanced CMOS NOR Flash Process

• Endurance of 20,000 Program/Erase Cycles

• Operation over Full Industrial Temperature Range

(–40°C to +85°C)

• IEEE Standard 1149.1/1532 Boundary-Scan (JTAG)

Support for Programming, Prototyping, and Testing

• JTAG Command Initiation of Standard FPGA

Configuration

• Cascadable for Storing Longer or Multiple Bitstreams

• Dedicated Boundary-Scan (JTAG) I/O Power Supply (V

CCJ

)

• I/O Pins Compatible with Voltage Levels Ranging From

1.8V to 3.3V

• Design Support Using the Xilinx ISE® Alliance and

Foundation™ Software Packages

• XCF01S/XCF02S/XCF04S

• 3.3V Supply Voltage

• Serial FPGA Configuration Interface

• Available in Small-Footprint VO20 and VOG20

Packages

• XCF08P/XCF16P/XCF32P

• 1.8V Supply Voltage

• Serial or Parallel FPGA Configuration Interface

• Available in Small-Footprint VOG48, FS48, and

FSG48 Packages

• Design Revision Technology Enables Storing and

Accessing Multiple Design Revisions for

Configuration

• Built-In Data Decompressor Compatible with Xilinx

Advanced Compression Technology

Description

Xilinx introduces the Platform Flash series of in-system

programmable configuration PROMs. Available in

1 to 32 Mb densities, these PROMs provide an easy-to-use,

cost-effective, and reprogrammable method for storing large

Xilinx FPGA configuration bitstreams. The Platform Flash

PROM series includes both the 3.3V XCFxxS PROM and

the 1.8V XCFxxP PROM. The XCFxxS version includes

4 Mb, 2 Mb, and 1 Mb PROMs that support Master Serial

and Slave Serial FPGA configuration modes (Figure 1,

page 2). The XCFxxP version includes 32 Mb, 16 Mb, and

8 Mb PROMs that support Master Serial, Slave Serial,

Master SelectMAP, and Slave SelectMAP FPGA

configuration modes (Figure 2, page 2).

When driven from a stable, external clock, the PROMs can

output data at rates up to 33 MHz. Refer to "AC Electrical

Characteristics," page 16 for timing considerations.

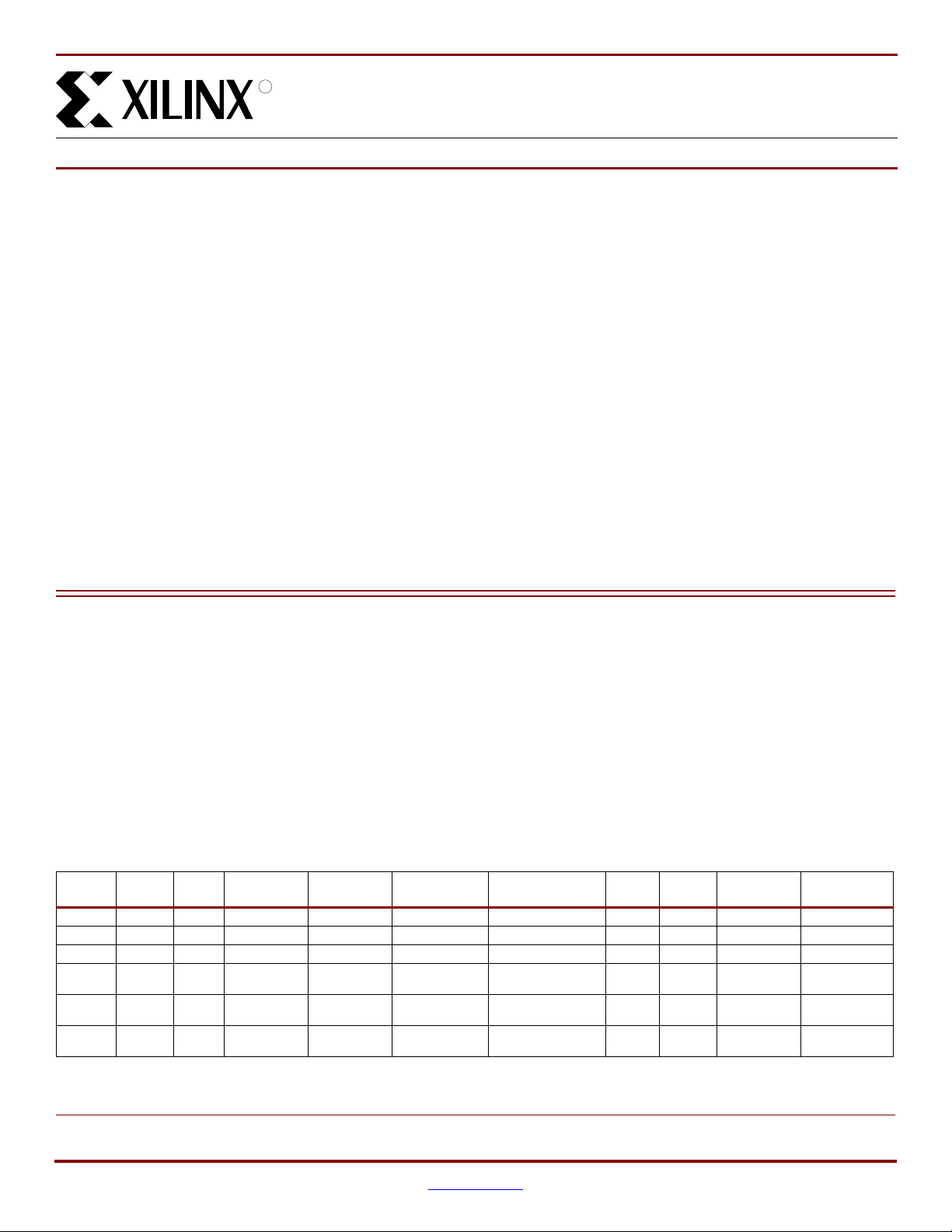

A summary of the Platform Flash PROM family members

and supported features is shown in Table 1.

35

Platform Flash In-System Programmable

Configuration PROMs

DS123 (v2.19) June 6, 2016 Product Specification

R

Table 1: Platform Flash PROM Features

Device

Density

(Mb)

V

CCINT

(V)

V

CCO

Range

(V)

V

CCJ

Range

(V)

Packages

Program In-system

via JTAG

Serial

Config.

Parallel

Config.

Design

Revisioning

Compression

XCF01S 1 3.3 1.8 – 3.3 2.5 – 3.3 VO20/VOG20

XCF02S 2 3.3 1.8 – 3.3 2.5 – 3.3 VO20/VOG20

XCF04S 4 3.3 1.8 – 3.3 2.5 – 3.3 VO20/VOG20

XCF08P 8 1.8 1.8 – 3.3 2.5 – 3.3

VO48/VOG48

FS48/FSG48

(1)

XCF16P 16 1.8 1.8 – 3.3 2.5 – 3.3

VO48/VOG48

FS48/FSG48

XCF32P 32 1.8 1.8 – 3.3 2.5 – 3.3

VO48/VOG48

FS48/FSG48

Notes:

1. XCF08P supports storage of a design revision only when cascaded with another XCFxxP PROM. See "Design Revisioning," page 8 for details.

页面指南