下载

DS054 (v2.5) May 22, 2009 www.xilinx.com

Product Specification 1

© 1998–2009 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are trademarks of Xilinx in the United States and other

countries. All other trademarks are the property of their respective owners.

k

Features

• Optimized for high-performance 3.3V systems

- 5 ns pin-to-pin logic delays, with internal system

frequency up to 208 MHz

- Small footprint packages including VQFPs, TQFPs

and CSPs (Chip Scale Package)

- Pb-free available for all packages

- Lower power operation

- 5V tolerant I/O pins accept 5V, 3.3V, and 2.5V

signals

- 3.3V or 2.5V output capability

- Advanced 0.35 micron feature size CMOS

FastFLASH technology

• Advanced system features

- In-system programmable

- Superior pin-locking and routability with

FastCONNECT II switch matrix

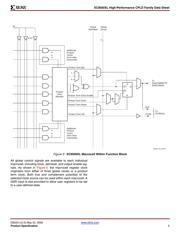

- Extra wide 54-input Function Blocks

- Up to 90 product-terms per macrocell with

individual product-term allocation

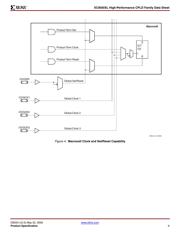

- Local clock inversion with three global and one

product-term clocks

- Individual output enable per output pin with local

inversion

- Input hysteresis on all user and boundary-scan pin

inputs

- Bus-hold circuitry on all user pin inputs

- Supports hot-plugging capability

- Full IEEE Std 1149.1 boundary-scan (JTAG)

support on all devices

• Four pin-compatible device densities

- 36 to 288 macrocells, with 800 to 6400 usable

gates

• Fast concurrent programming

• Slew rate control on individual outputs

• Enhanced data security features

• Excellent quality and reliability

- 10,000 program/erase cycles endurance rating

- 20 year data retention

• Pin-compatible with 5V core XC9500 family in common

package footprints

0

XC9500XL High-Performance CPLD

Family Data Sheet

DS054 (v2.5) May 22, 2009

00

Product Specification

R

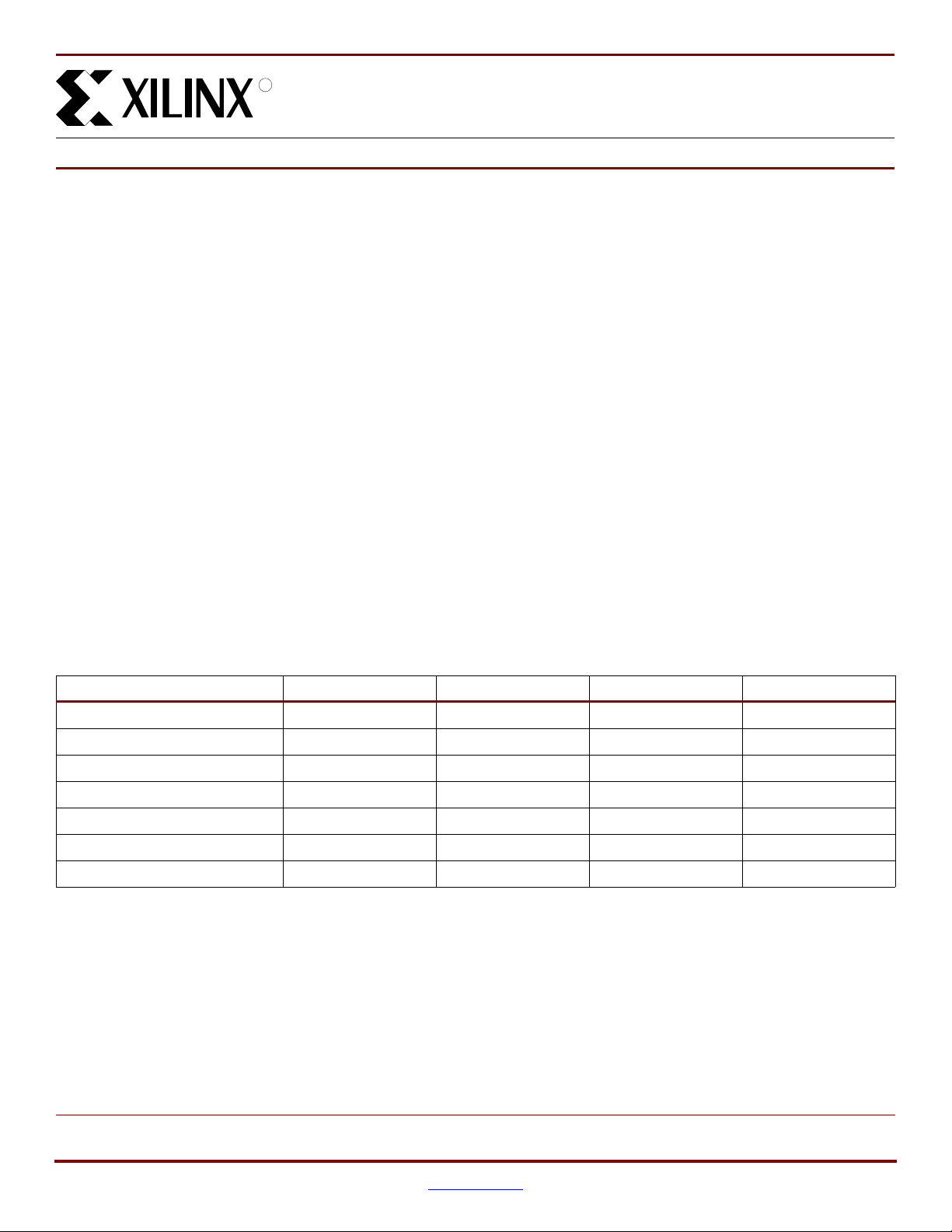

Table 1: XC9500XL Device Family

XC9536XL XC9572XL XC95144XL XC95288XL

Macrocells 36 72 144 288

Usable Gates 800 1,600 3,200 6,400

Registers 36 72 144 288

T

PD

(ns) 5556

T

SU

(ns) 3.7 3.7 3.7 4.0

T

CO

(ns) 3.5 3.5 3.5 3.8

f

SYSTEM

(MHz) 178 178 178 208