Flash-Erasable Reprogrammable

CMOS PAL

®

Device

PALCE20V8

USE ULTRA37000

TM

FOR

ALL NEW DESIGNS

Cypress Semiconductor Corporation • 3901 North First Street • San Jose, CA 95134 • 408-943-2600

Document #: 38-03026 Rev. *B Revised April 19, 2004

Features

• Active pull-up on data input pins

• Low power version (20V8L)

— 55 mA max. commercial (15, 25 ns)

— 65 mA max. military/industrial

(15, 25 ns)

• Standard version has low power

— 90 mA max. commercial

(15, 25 ns)

— 115 mA max. commercial (10 ns)

— 130 mA max. military/industrial (15, 25 ns)

• CMOS Flash technology for electrical erasability and

reprogrammability

• User-programmable macrocell

— Output polarity control

— Individually selectable for registered or combina-

torial operation

• QSOP package available

— 10, 15, and 25 ns com’l version

— 15, and 25 ns military/industrial versions

• High reliability

— Proven Flash technology

— 100% programming and functional testing

Functional Description

The Cypress PALCE20V8 is a CMOS Flash Erasable

second-generation programmable array logic device. It is

implemented with the familiar sum-of-product (AND-OR) logic

structure and the programmable macrocell.

The PALCE20V8 is executed in a 24-pin 300-mil molded DIP,

a 300-mil cerdip, a 28-lead square ceramic leadless chip

carrier, a 28-lead square plastic leaded chip carrier, and a

24-lead quarter size outline. The device provides up to 20

inputs and 8 outputs. The PALCE20V8 can be electrically

erased and reprogrammed. The programmable macrocell

enables the device to function as a superset to the familiar

24-pin PLDs such as 20L8, 20R8, 20R6, 20R4.

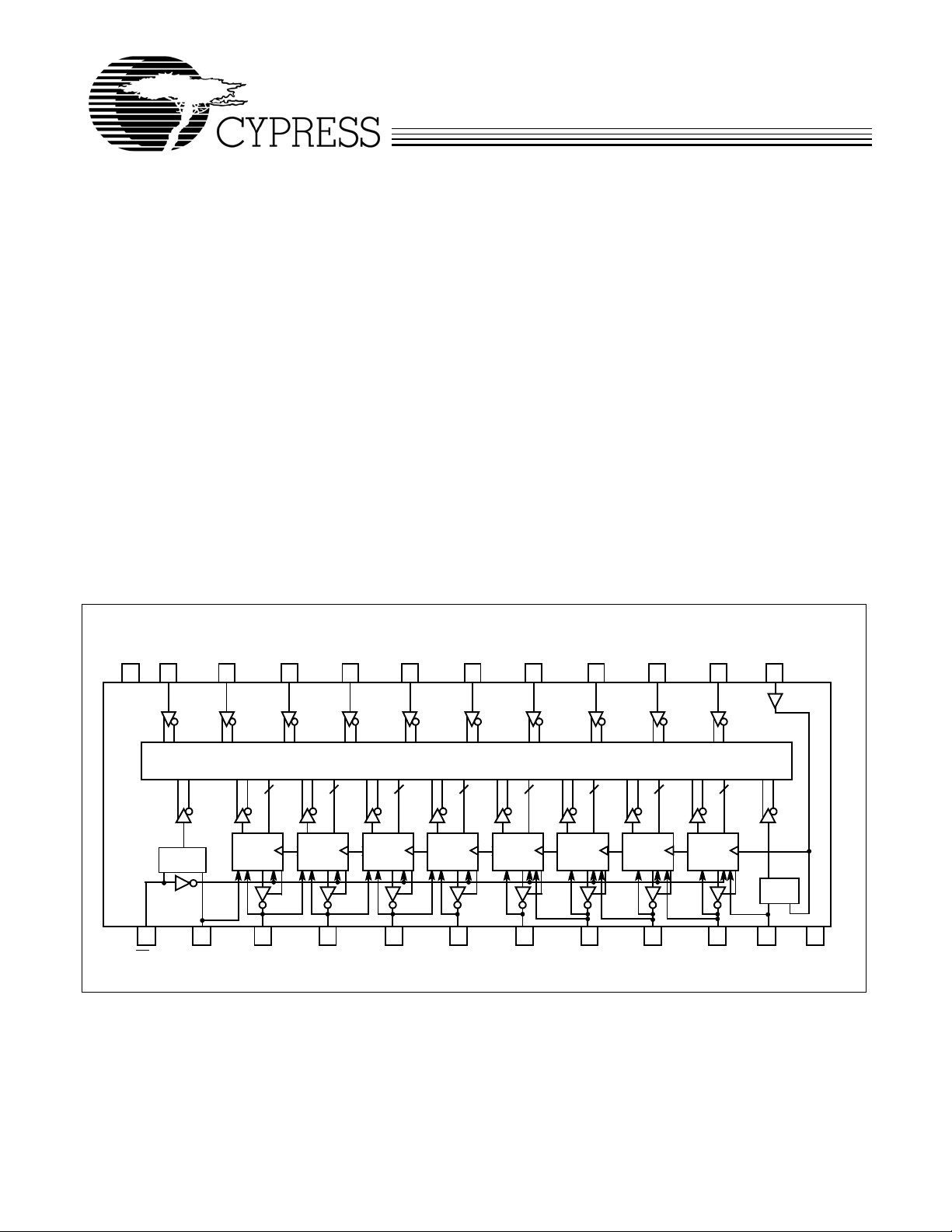

LogicBlockDiagram(PDIP/CDIP/QSOP)

8888888 8

10987654321

13 15 16 17 18 19 20 21 22 23

PROGRAMMABLE

AND ARRAY

(64 x

40)

Macrocell Macrocell Macrocell Macrocell Macrocell Macrocell Macrocell Macrocell

I

9

I

8

I

7

I

6

I

5

I

4

I

3

I

2

I

1

CLK/I

0

OE/I

11

I/O

0

I/O

1

I/O

2

I/O

3

I/O

4

I/O

5

I/O

6

I/O

7

I

13

12

GND

11

I

10

MUX

24

V

CC

MUX

14

I

12

[+] Feedback