下载

PRODUCTPREVIEW

OS OUTN

VDDOE

GND OUTP

FS0

FS1

1 6

2 5

43

7

8

LMK61PD0A2

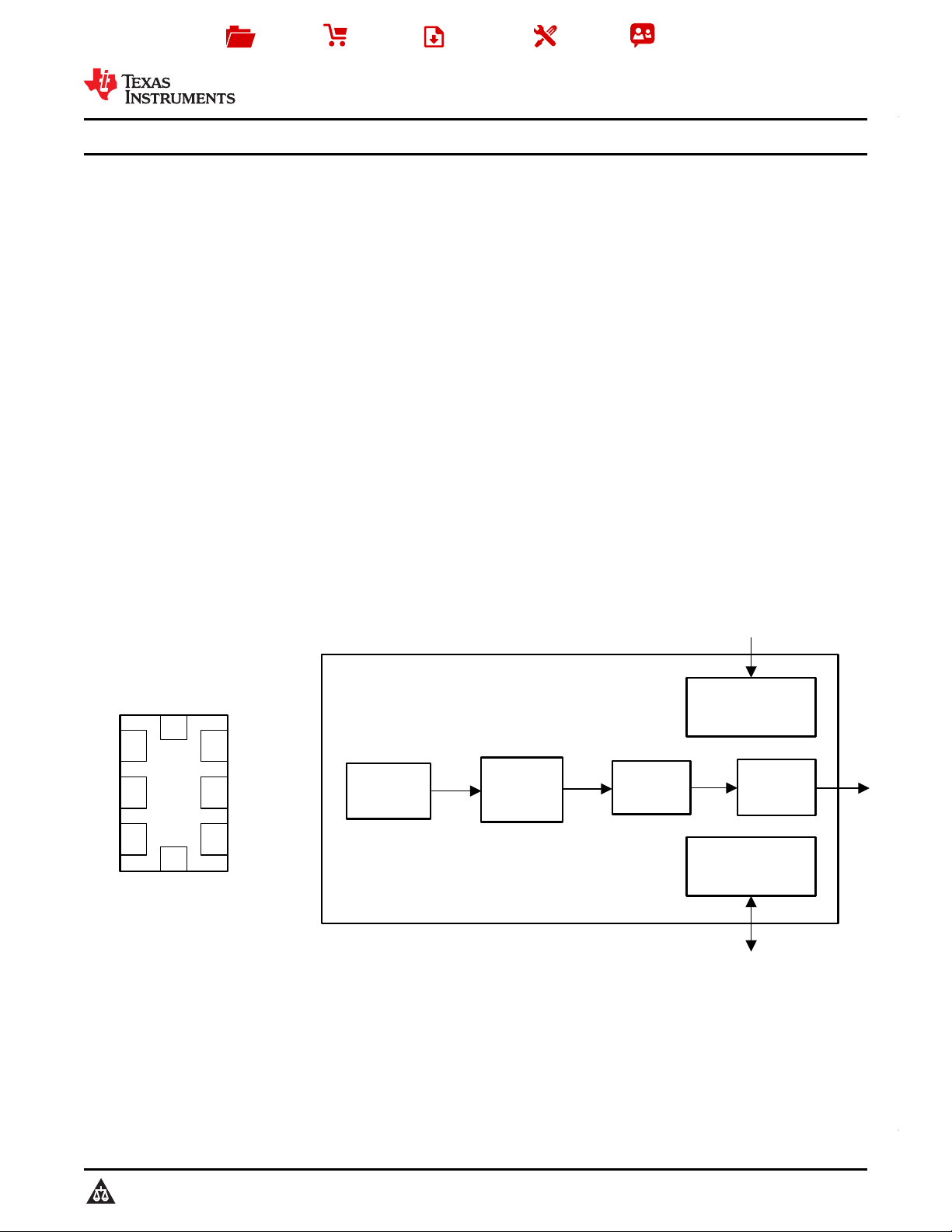

Ultra-high performance oscillator

PLL

Output

Divider

Output

Buffer

Power Conditioning

Interface

ROM (Pin Control)

Integrated

Oscillator

Product

Folder

Sample &

Buy

Technical

Documents

Tools &

Software

Support &

Community

LMK61PD0A2

SNAS675 –OCTOBER 2015

LMK61PD0A2 Ultra-Low Jitter Pin Programmable Oscillator

1 Features 2 Applications

1

• Ultra-low Noise, High Performance

• High-performance replacement for crystal-, SAW-,

or silicon-based Oscillators

– Jitter: 90 fs RMS typical f

OUT

> 100 MHz

• Switches, Routers, Network Line Cards, Base

– PSRR: -70 dBc, robust supply noise immunity

Band Units (BBU), Servers, Storage/SAN

• Flexible Output Frequency and Format; User

• Test and Measurement

Selectable

• Medical Imaging

– Frequencies: 62.5 MHz, 100 MHz, 106.25

• FPGA, Processor Attach

MHz, 125 MHz, 156.25 MHz, 212.5 MHz,

312.5 MHz

3 Description

– Formats: LVPECL, LVDS or HCSL

The LMK61PD0A2 is an ultra-low jitter PLLatinum

TM

• Total frequency tolerance of ± 50 ppm

pin-programmable oscillator that generates commonly

• Internal memory stores multiple start-up

used reference clocks. The device is pre-

configurations, selectable through pin control

programmed in factory to support seven unique

reference clock frequencies that can be selected by

• 3.3V operating voltage

pin-strapping each of FS[1:0] to VDD, GND or NC (no

• Industrial temperature range (-40ºC to +85ºC)

connect). Output format is selected between

• 7 mm x 5 mm 8-pin package

LVPECL, LVDS, or HCSL by pin-strapping OS to

VDD, GND or NC. Internal power conditioning provide

excellent power supply ripple rejection (PSRR),

reducing the cost and complexity of the power

delivery network. The device operates from a single

3.3 V ± 5% supply.

Pinout and Simplified Block Diagram

1

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCT PREVIEW Information. Product in design phase of

development. Subject to change or discontinuance without notice.