下载

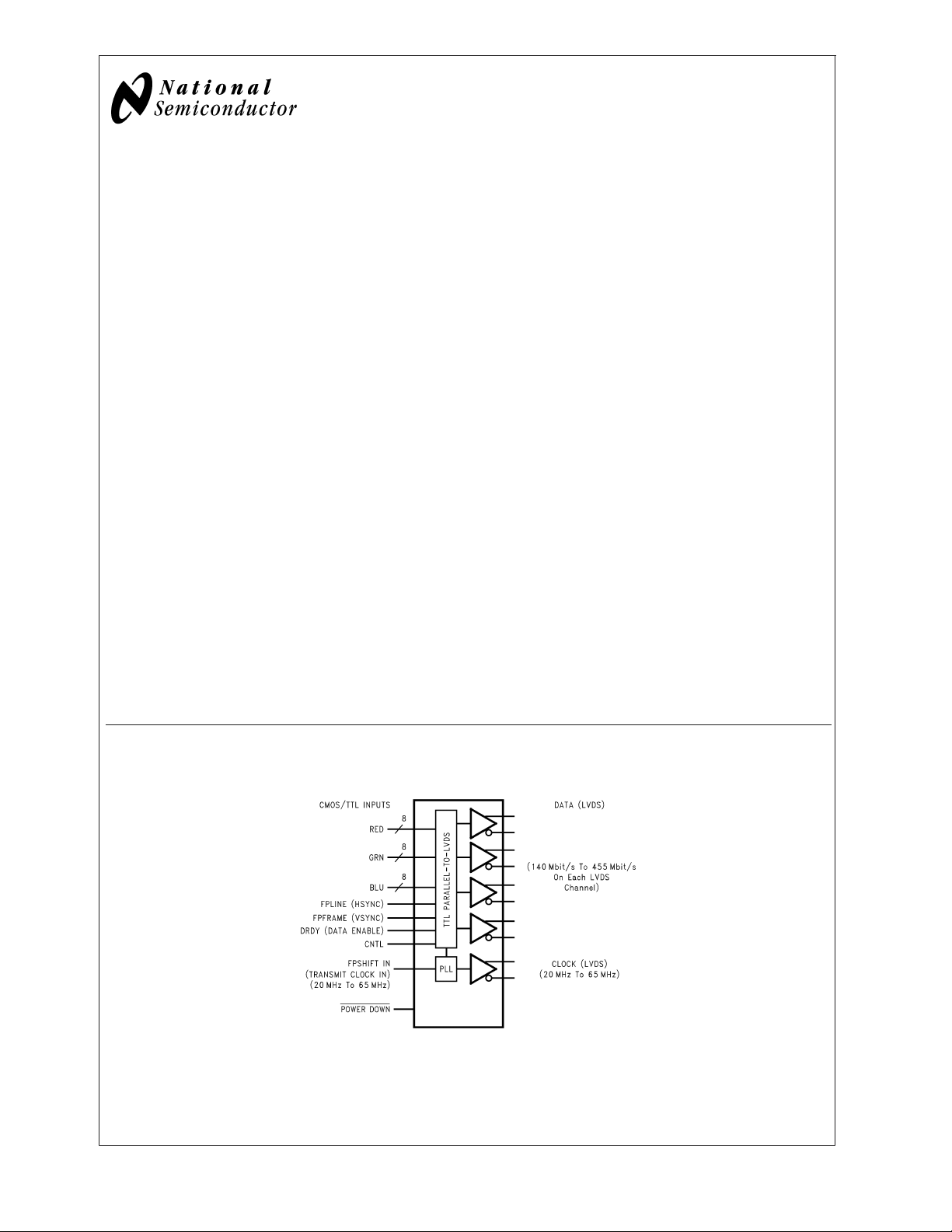

DS90C383B

+3.3V Programmable LVDS Transmitter 24-Bit Flat Panel

Display (FPD) Link-65 MHz

General Description

The DS90C383B transmitter converts 28 bits of CMOS/TTL

data into four LVDS (Low Voltage Differential Signaling) data

streams. A phase-locked transmit clock is transmitted in

parallel with the data streams over a fifth LVDS link. Every

cycle of the transmit clock 28 bits of input data are sampled

and transmitted. At a transmit clock frequency of 65 MHz, 24

bits of RGB data and 3 bits of LCD timing and control data

(FPLINE, FPFRAME, DRDY) are transmitted at a rate of 455

Mbps per LVDS data channel. Using a 65 MHz clock, the

data throughput is 227 Mbytes/sec. The DS90C383B trans-

mitter can be programmed for Rising edge strobe or Falling

edge strobe through a dedicated pin. A Rising edge or

Falling edge strobe transmitter will interoperate with a Falling

edge strobe Receiver (DS90CF386) without any translation

logic.

This chipset is an ideal means to solve EMI and cable size

problems associated with wide, high speed TTL interfaces.

Features

n No special start-up sequence required between

clock/data and /PD pins. Input signal (clock and data)

can be applied either before or after the device is

powered.

n Support Spread Spectrum Clocking up to 100kHz

frequency modulation & deviations of

±

2.5% center

spread or −5% down spread.

n "Input Clock Detection" feature will pull all LVDS pairs to

logic low when input clock is missing and when /PD pin

is logic high.

n 18 to 68 MHz shift clock support

n Best–in–Class Set & Hold Times on TxINPUTs

n Tx power consumption

<

130 mW (typ)

@

65MHz

Grayscale

n 40% Less Power Dissipation than BiCMOS Alternatives

n Tx Power-down mode

<

60µW (typ)

n Supports VGA, SVGA, XGA and Dual Pixel SXGA.

n Narrow bus reduces cable size and cost

n Up to 1.8 Gbps throughput

n Up to 227 Megabytes/sec bandwidth

n 345 mV (typ) swing LVDS devices for low EMI

n PLL requires no external components

n Compatible with TIA/EIA-644 LVDS standard

n Low profile 56-lead TSSOP package

n Improved replacement for:

SN75LVDS83, DS90C383A

Block Diagram

DS90C383B

20098401

Order Number DS90C383BMT

See NS Package Number MTD56

TRI-STATE

®

is a registered trademark of National Semiconductor Corporation.

PRELIMINARY

July 2004

DS90C383B +3.3V Programmable LVDS Transmitter 24-Bit Flat Panel Display (FPD) Link-65 MHz

© 2004 National Semiconductor Corporation DS200984 www.national.com

页面指南