下载

Rev. 0.6 1/12 Copyright © 2012 by Silicon Labs Si531x/2x-EVB

Si5316-EVB Si5319-EVB

Si5322/23-EVB Si5324-EVB

Si5325/26-EVB Si5327-EVB

Si5316, Si5319, Si5322/23, Si5324, Si5325/26,

AND

Si5327 EVB U

SER

’

S

G

UIDE

1. Introduction

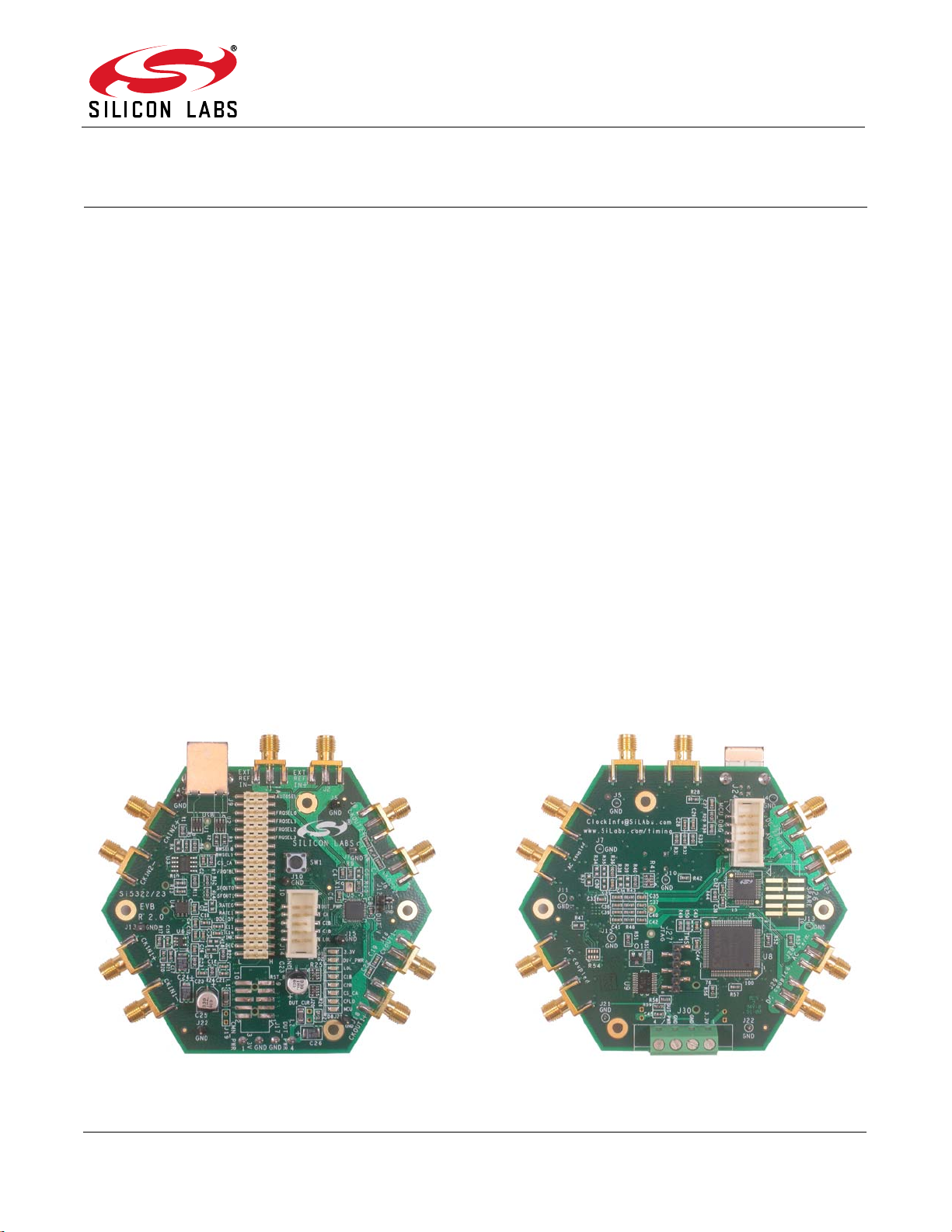

The Si5316-EVB, Si5319-EVB, Si5322/23-EVB, Si5324-EVB, Si5325/26-EVB, and Si5327-EVB provide platforms

for evaluating Silicon Laboratories' Si5316, Si5319, Si5322/Si5323, Si5324, Si5325/Si5326, and Si5327

Any-Frequency Precision Clock Timing ICs. The Si5316, Si5322, and Si5323 are controlled directly using

configuration pins on the devices, while the Si5319, Si5324, Si5325, Si5326, and Si5327 are controlled by a

microprocessor or MCU (micro-controller unit) via an I

2

C or SPI interface. The Si5316 is a jitter attenuator with a

loop bandwidth ranging from 60 Hz to 8.4 kHz. The Si5322 and Si5325 are low jitter clock multipliers with a loop

bandwidth ranging from 30 kHz to 1.3 MHz. The Si5319, Si5323, and Si5326 are jitter-attenuating clock multipliers,

with a loop bandwidth ranging from 60 Hz to 8.4 kHz. The Si5324 and Si5327 have features and capabilities very

similar to the Si5326, but they have much lower loop bandwidths that range from 4 to 525 Hz. The Si5326 device

can optionally be configured to operate as a Si5325, so a single evaluation board is available to evaluate both

devices. Likewise, the Si5323 can be configured to operate as a Si5322, so the two devices share a single

evaluation board.

The Si531x/2x Any-Frequency Precision Clocks are based on Silicon Laboratories' third-generation DSPLL

®

technology, which provides any-frequency synthesis in a highly integrated PLL solution that eliminates the need for

external VCXO and loop filter components. The devices have excellent phase noise and jitter performance. The

Si5316 is a jitter attenuator that supports jitter generation of 0.3 ps RMS (typ) across the 12 kHz–20 MHz and

50 kHz–80 MHz jitter filter bandwidths. The Si5319, Si5323, and Si5326 jitter attenuating clock multipliers support

jitter generation of 0.3 ps RMS (typ) across the 12 kHz–20 MHz and 50 kHz–80 MHz jitter filter bandwidths. The

Si5324 and Si5327 are jitter attenuating clock multipliers supporting jitter attenuation of 0.3 ps RMS (typ) and

0.5 ps RMS (typ) across the 12 kHz to 20 MHz and 50 kHz to 80 MHz bands. The Si5322 and Si5325 support jitter

generation of 0.6 ps RMS (typ) across the 12 kHz–20 MHz and 50 kHz–80 MHz jitter filter bandwidths. For all

devices, the DSPLL loop bandwidth is digitally programmable, providing jitter performance optimization at the

application level. These devices are ideal for providing clock multiplication/clock division, jitter attenuation, and

clock distribution in mid-range and high-performance timing applications.

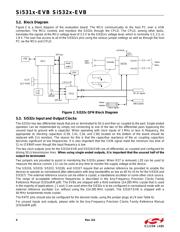

Figure 1. Si532x QFN EVB