下载

www.issi.com • Part Decoder • 2014

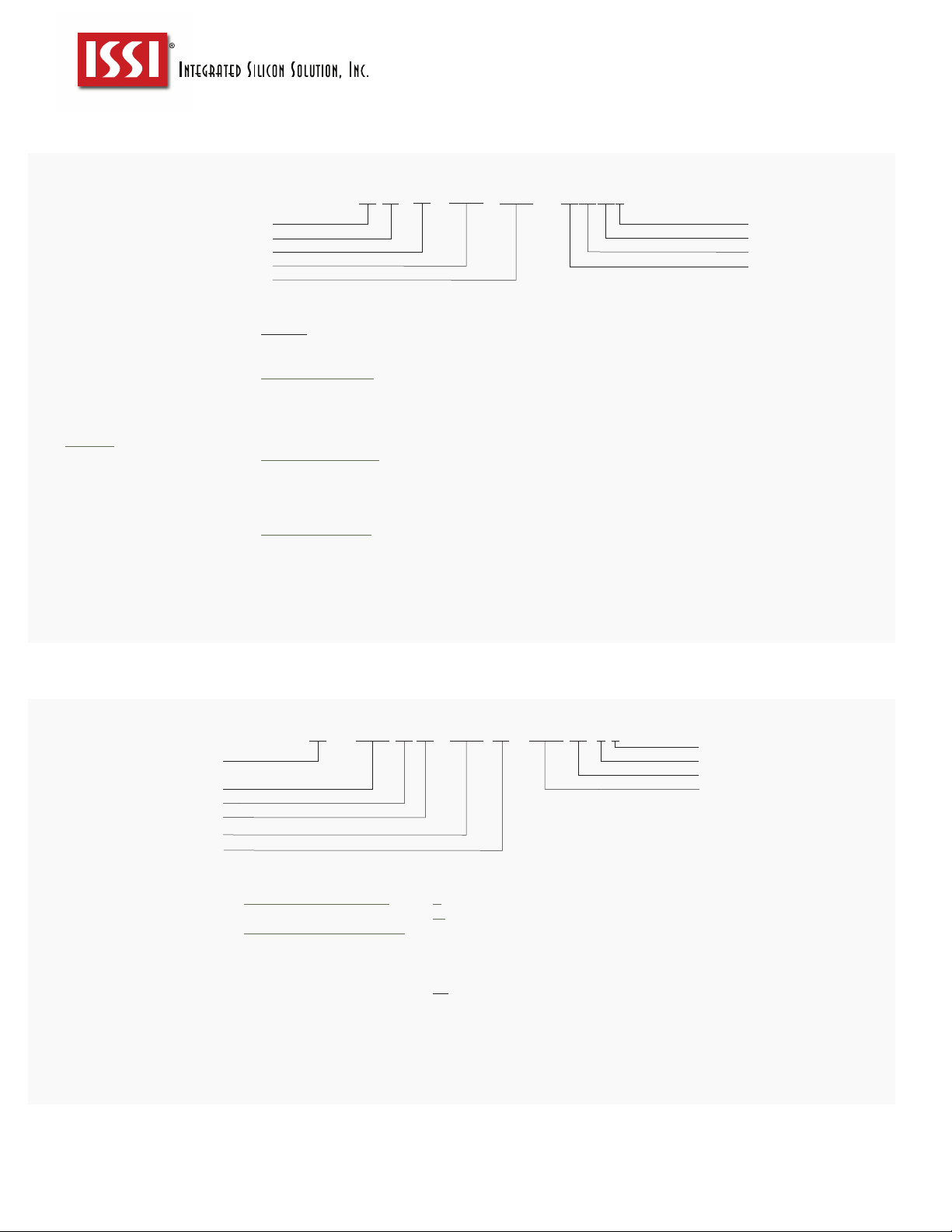

SRAM Part Decoder

QUAD/P, DDR-ll/P Part Decoder

IS 61 WV 12816 DBLL - 10 T L I

• SRAM Product Family

61/63 = High Speed

62 = Low Power

64 = Automotive High Speed

65 = Automotive Low Power

66 = Pseudo SRAM

67 = Automotive PSRAM

• Density/Configuration

Example:

25636 = 256Kx36

51216 = 512Kx16

1M36 = 1Mx36

• Die Rev/Voltage Range

Die Rev

Blank-Z

Voltage Range (WV)

ALL = 1.65V to 2.2V

BLL = 2.5V to 3.6V

• Solder Type

Blank = SnPb

L = Lead-free (RoHS Compliant)

• Package Code

B, B1, B2, B3 = BGA

CT = Copper TSOP

H = sTSOP

J = 300-mil SOJ

K = 400-mil SOJ

LQ = LQFP

M, M3, = BGA

Q = SOP

T/T2 = TSOP

TQ = TQFP

U = SOP

• Speed (ns or MHz)

Example:

8 = 8ns

200 = 200MHz

• Temp. Grade

Blank = Commercial Grade ( 0C to +70°C )

I = Industrial Grade ( -40C to +85°C )

A1 = Automotive Grade (-40C to +85°C)

A2 = Automotive Grade (-40C to +105°C)

A3 = Automotive Grade (-40C to +125°C)

• Operating Voltage Range/ Product Type

Asynchronous SRAM

C = 5V

LV = 3.3V

WV = Wide Voltage Range

Synchronous SRAM

P = Pipeline, F = Flowthrough

NLP/NLF/NVP/NVF = No-Wait Option

LP/LF: Vcc = 3.3V, VccQ = 3.3V/2.5V

VP/VF: Vcc = 2.5V, VccQ = 2.5V

QD = QUAD, DD = DDR-II Common I/O: Vcc = 1.8V , VccQ = 1.8V/1.5V

ISSI prefix

Product Family

Operating Voltage Range/Product Type

Density/Configuration

Die Rev/Voltage Range

Temp. Grade

Solder Type

Package Code

Speed (ns or MHz)

SRAM Part Decoder

IS 61 QDP 2 B4 4M18 A1 - 333 M3 L I

• Product Type

QD = QUAD

QDP = QUADP

DD = DDR-II, Common I/O

DDP = DDR-IIP, Common I/O

• Configuration

51236 = 512Kb x 36

1M18 = 1Mb x 18

1M36 = 1Mb x 36

2M18 = 2Mb x 18

2M36 = 2Mb x 36

4M18 = 4Mb x 18

• Read Latency (RL):

For QUAD/DDR-II devices:

Blank = 1.5 clock cycles

For QUADP/DDR-IIP devices:

Blank = 2.5 clock cycles

2 = 2.0 clock cycles

• ODT Option (if supported):

A: No ODT

A1: ODT Option 1

If ODT = HIGH or floating, a high range

termination resistance is selected.

If ODT = LOW, a low range

termination resistance is selected.

A2: ODT Option 2

If ODT = HIGH, a high range

termination resistance is selected.

If ODT = LOW or floating, ODT is disabled

• Speed

Example: 250 = 250MHz

• Package Code

B4 = 165 ball BGA (13 x 15 mm)

M3 = 165-ball BGA (15 x 17 mm)

• RoHS Version

Blank = Leaded

L = Lead-free

• Temperature Range

Blank = Commercial (0C to 70°C)

I = Industrial (-40C to 85°C)

• Burst Type:

B2 = Burst 2

B4 = Burst 4

ISSI prefix

Product Type

Read Latency

Burst Type

Configuration

ODT Option

Temp. Grade

RoHS Version

Package Code

Speed (MHz)