下载

Quad 16-/14-/12-Bit nanoDAC+

with 2 ppm/°C Reference, I

2

C Interface

Data Sheet

AD5696R/AD5695R/AD5694R

Rev. C Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 ©2012–2014 Analog Devices, Inc. All rights reserved.

Technical Support www.analog.com

FEATURES

High relative accuracy (INL): ±2 LSB maximum at 16 bits

Low drift 2.5 V reference: 2 ppm/°C typical

Tiny package: 3 mm × 3 mm, 16-lead LFCSP

Total unadjusted error (TUE): ±0.1% of FSR maximum

Offset error: ±1.5 mV maximum

Gain error: ±0.1% of FSR maximum

High drive capability: 20 mA, 0.5 V from supply rails

User selectable gain of 1 or 2 (GAIN pin)

Reset to zero scale or midscale (RSTSEL pin)

1.8 V logic compatibility

Low glitch: 0.5 nV-sec

400 kHz I

2

C-compatible serial interface

Robust 3.5 kV HBM and 1.5 kV FICDM ESD rating

Low power: 3.3 mW at 3 V

2.7 V to 5.5 V power supply

−40°C to +105°C temperature range

APPLICATIONS

Optical transceivers

Base-station power amplifiers

Process control (PLC I/O cards)

Industrial automation

Data acquisition systems

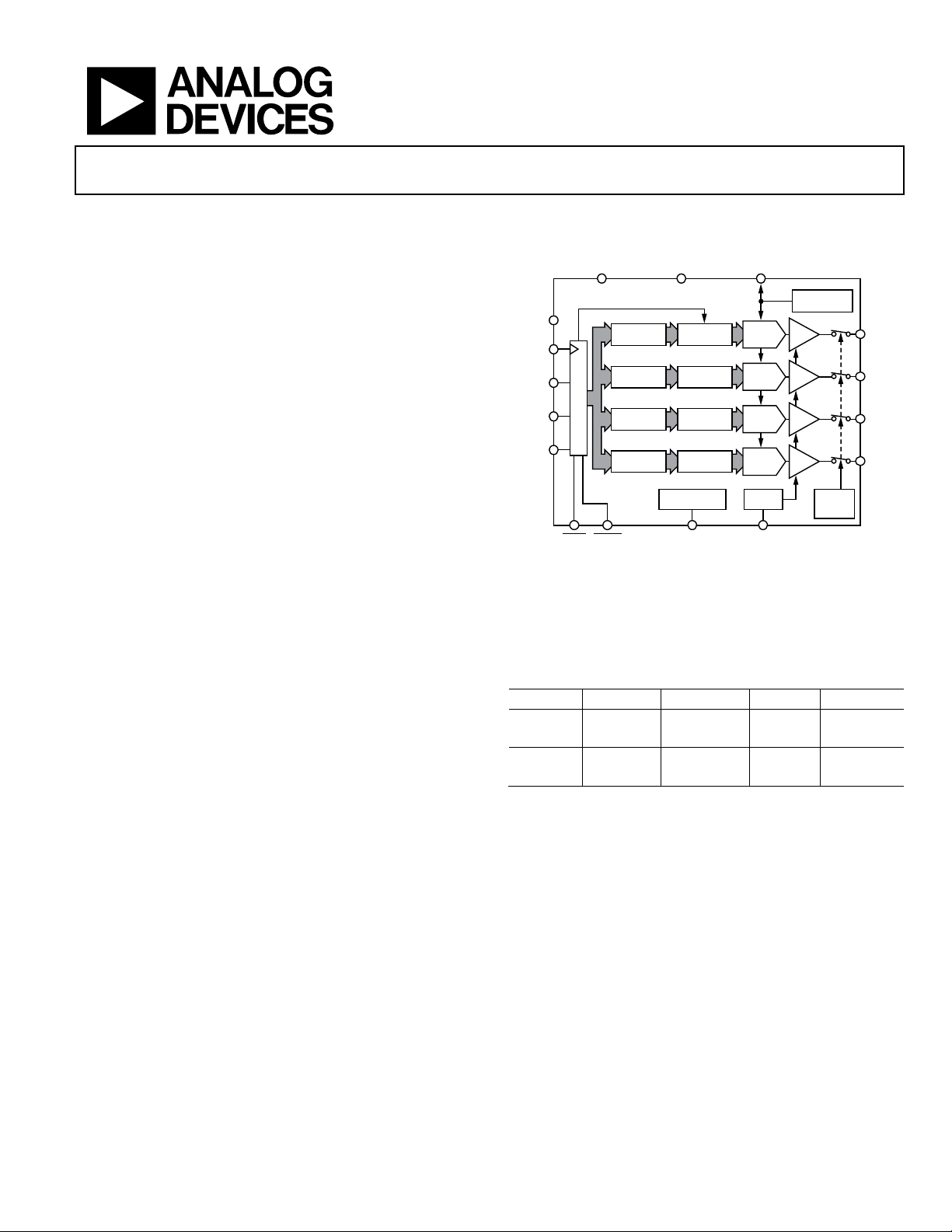

FUNCTIONAL BLOCK DIAGRAM

Figure 1.

GENERAL DESCRIPTION

The AD5696R/AD5695R/AD5694R family are low power, quad,

16-/14-/12-bit buffered voltage output DACs. The devices include

a 2.5 V, 2 ppm/°C internal reference (enabled by default) and a

gain select pin giving a full-scale output of 2.5 V (gain = 1) or 5

V (gain = 2). All devices operate from a single 2.7 V to 5.5 V

supply, are guaranteed monotonic by design, and exhibit less

than 0.1% FSR gain error and 1.5 mV offset error performance.

The devices are available in a 3 mm × 3 mm LFCSP and a

TSSOP package.

The AD5696R/AD5695R/AD5694R also incorporate a power-

on reset circuit and a RSTSEL pin that ensures that the DAC

outputs power up to zero scale or midscale and remain there

until a valid write takes place. Each part contains a per-channel

power-down feature that reduces the current consumption of

the device to 4 μA at 3 V while in power-down mode.

The AD5696R/AD5695R/AD5694R use a versatile 2-wire serial

interface that operates at clock rates up to 400 kHz, and

includes a V

LOGIC

pin intended for 1.8 V/3 V/5 V logic.

Table 1. Quad nanoDAC+ Devices

Interface Reference 16-Bit 14-Bit 12-Bit

SPI Internal AD5686R AD5685R AD5684R

External AD5686 AD5684

I

2

C Internal AD5696R AD5695R AD5694R

External AD5696 AD5694

PRODUCT HIGHLIGHTS

1. High Relative Accuracy (INL).

AD5696R (16-bit): ±2 LSB maximum

AD5695R (14-bit): ±1 LSB maximum

AD5694R (12-bit): ±1 LSB maximum

2. Low Drift 2.5 V On-Chip Reference.

2 ppm/°C typical temperature coefficient

5 ppm/°C maximum temperature coefficient

3. Two Package Options.

3 mm × 3 mm, 16-lead LFCSP

16-lead TSSOP

SCL

V

LOGIC

SDA

A1

A0

INPUT

REGISTER

DAC

REGISTER

STRING

DAC A

BUFFER

V

OUT

A

INPUT

REGISTER

DAC

REGISTER

STRING

DAC B

BUFFER

V

OUT

B

INPUT

REGISTER

DAC

REGISTER

STRING

DAC C

BUFFER

V

OUT

C

INPUT

REGISTER

DAC

REGISTER

STRING

DAC D

BUFFER

V

OUT

D

V

REF

GND

V

DD

2.5V

REFERENCE

POWER-

DOWN

LOGIC

POWER-ON

RESET

GAIN =

×1/×2

INTERFACE LOGIC

RSTSEL GAINLDAC RESET

AD5696R/AD5695R/AD5694R

10486-001

页面指南