下载

TMS320C6712

FLOATING-POINT DIGITAL SIGNAL PROCESSOR

SPRS148 – AUGUST 2000

1

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

Best Price/Performance Floating-Point

Digital Signal Processor (DSP)

TMS320C6712

– 10-ns Instruction Cycle Time

– 100-MHz Clock Rate

– Eight 32-Bit Instructions/Cycle

– 600 MFLOPS

– C6712 and C6211/C6711 are

Pin-Compatible

VelociTI Advanced Very Long Instruction

Word (VLIW) C67x DSP Core

– Eight Highly Independent Functional

Units:

– Four ALUs (Floating- and Fixed-Point)

– Two ALUs (Fixed-Point)

– Two Multipliers (Floating- and

Fixed-Point)

– Load-Store Architecture With 32 32-Bit

General-Purpose Registers

– Instruction Packing Reduces Code Size

– All Instructions Conditional

Instruction Set Features

– Hardware Support for IEEE

Single-Precision and Double-Precision

Instructions

– Byte-Addressable (8-, 16-, 32-Bit Data)

– 8-Bit Overflow Protection

– Saturation

– Bit-Field Extract, Set, Clear

– Bit-Counting

– Normalization

L1/L2 Memory Architecture

– 32K-Bit (4K-Byte) L1P Program Cache

(Direct Mapped)

– 32K-Bit (4K-Byte) L1D Data Cache

(2-Way Set-Associative)

– 512K-Bit (64K-Byte) L2 Unified Mapped

RAM/Cache

(Flexible Data/Program Allocation)

– 1024M-Byte Addressable External

Memory Space

Device Configuration

– Boot Mode: 8- and 16-Bit ROM Boot

– Endianness: Little Endian, Big Endian

16-Bit External Memory Interface (EMIF)

– Glueless Interface to Synchronous

Memories: SDRAM and SBSRAM

– Glueless Interface to Asynchronous

Memories: SRAM and EPROM

Enhanced Direct-Memory-Access (EDMA)

Controller

Two Multichannel Buffered Serial Ports

(McBSPs)

– Direct Interface to T1/E1, MVIP, SCSA

Framers

– ST-Bus-Switching Compatible

– Up to 256 Channels Each

– AC97-Compatible

– Serial-Peripheral-Interface (SPI)

Compatible (Motorola)

Two 32-Bit General-Purpose Timers

Flexible Phase-Locked-Loop (PLL) Clock

Generator

IEEE-1149.1 (JTAG

†

)

Boundary-Scan-Compatible

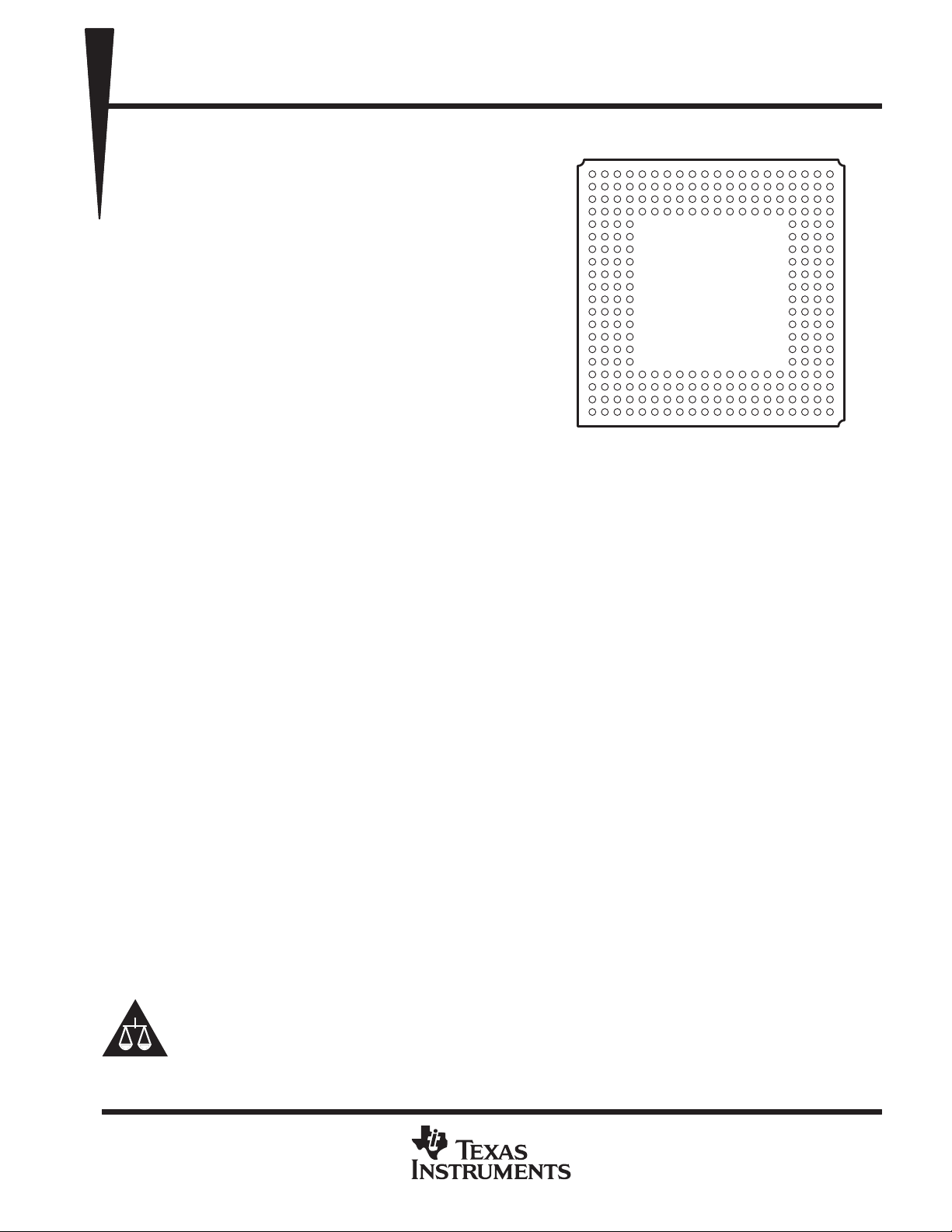

256-Pin Ball Grid Array (BGA) Package

(GFN Suffix)

0.18-µm/5-Level Metal Process

– CMOS Technology

3.3-V I/Os, 1.8-V Internal

PR

O

DU

C

T PREVIEW

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Copyright 2000, Texas Instruments Incorporated

PRODUCT PREVIEW information concerns products in the formative or

design phase of development. Characteristic data and other

specifications are design goals. Texas Instruments reserves the right to

change or discontinue these products without notice.

VelociTI and C67x are trademarks of Texas Instruments.

Motorola is a trademark of Motorola, Inc.

†

IEEE Standard 1149.1-1990 Standard-Test-Access Port and Boundary Scan Architecture.

1915 1713119

Y

V

T

U

P

N

R

W

75

L

J

K

H

F

G

31

D

B

C

A

E

M

2468 201816141210

GFN 256-PIN BALL GRID ARRAY (BGA) PACKAGE

(BOTTOM VIEW)