© Semiconductor Components Industries, LLC, 2016

August, 2016 − Rev. 10

1 Publication Order Number:

MC100EPT24/D

MC100EPT24

3.3V LVTTL/LVCMOS to

Differential LVECL Translator

Description

The MC100EPT24 is a LVTTL/LVCMOS to differential LVECL

translator. Because LVECL levels and LVTTL/LVCMOS levels are

used, a −3.3 V, +3.3 V and ground are required. The small outline

8-lead package and the single gate of the EPT24 makes it ideal for

those applications where space, performance, and low power are at a

premium.

Features

• 350 ps Typical Propagation Delay

• Maximum Input Clock Frequency = > 1.0 GHz Typical

• The 100 Series Contains Temperature Compensation

• Operating Range:

V

CC

= 3.0 V to 3.6 V; V

EE

= −3.6 V to −3.0 V; GND = 0 V

• PNP LVTTL Input for Minimal Loading

• Q Output will Default HIGH with Input Open

• These Devices are Pb-Free, Halogen Free and are RoHS Compliant

www.onsemi.com

*For additional marking information, refer to

Application Note AND8002/D

.

(Note: Microdot may be in either location)

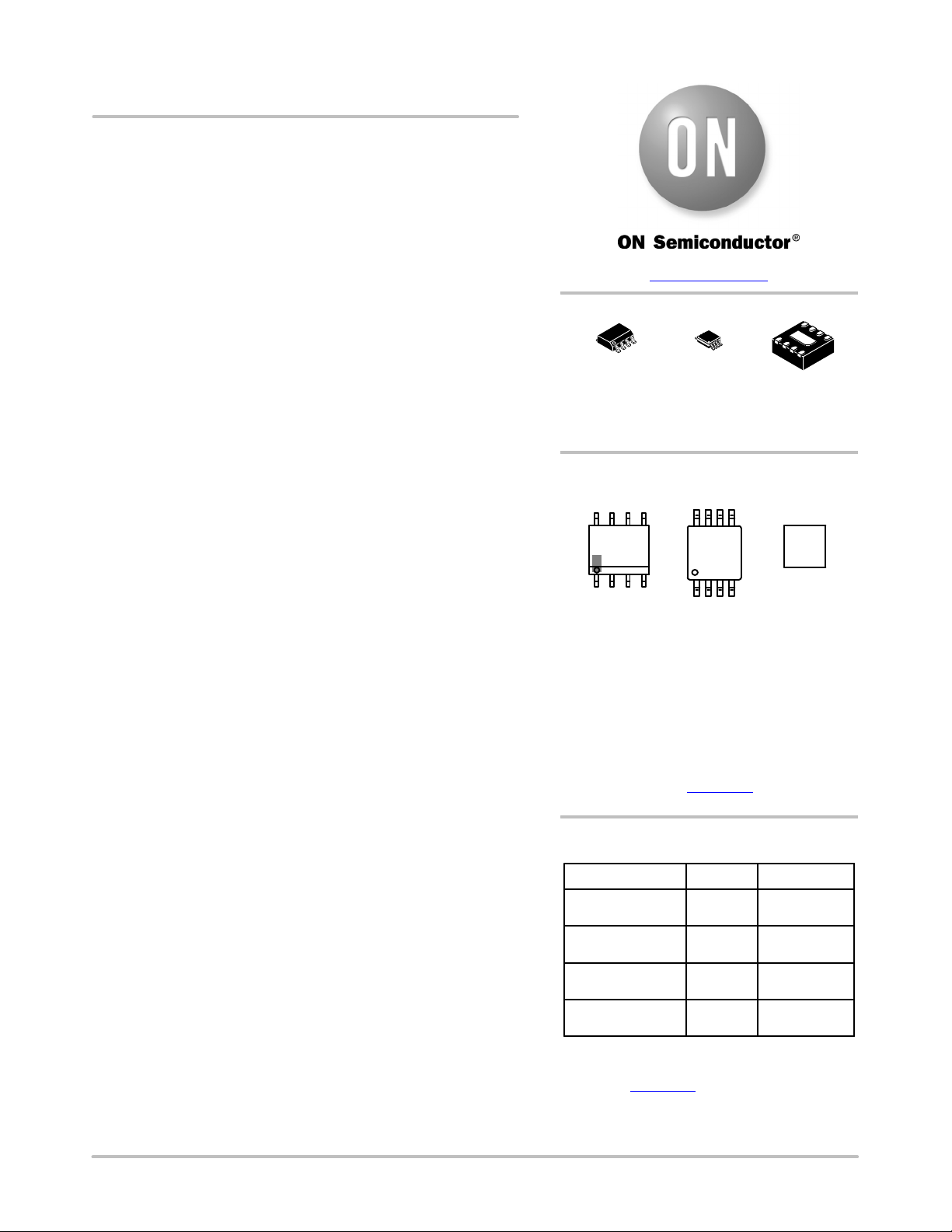

ORDERING INFORMATION

Device Package Shipping†

MC100EPT24DG SOIC−8 NB

(Pb-Free)

98 Units / Tube

MC100EPT24DR2G

2500 Tape & Reel

TSSOP−8

(Pb-Free)

MC100EPT24MNR4G 1000 Tape & Reel

MC100EPT24DTG 100 Units / Tube

SOIC−8 NB

(Pb-Free)

DFN8

(Pb-Free)

†For information on tape and reel specifications, in-

cluding part orientation and tape sizes, please refer

to our Tape and Reel Packaging Specifications

Brochure, BRD8011/D

.

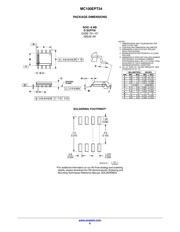

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

M = Date Code

G = Pb-Free Package

SOIC−8 NB

D SUFFIX

CASE 751−07

MARKING DIAGRAMS*

TSSOP−8

DT SUFFIX

CASE 948R−02

ALYWG

G

KA24

1

8

1

8

1

8

KPT24

ALYW

G

1

8

3U MG

G

14

SOIC−8 NB TSSOP−8 DFN8

DFN8

MN SUFFIX

CASE 506AA

页面指南