下载

1

www.pericom.com PI6LC48H02-01 Rev B 09/23/2015All trademarks are property of their respective owners.

PI6LC48H02-01

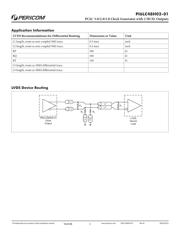

Block Diagram

Phase

Lock

Loop

Crystal

Driver

VDD

GND

X1/CLK

X2

25 MHz

crystal or clock

Control

Logic

S1:S0

2

CLK0

CLK0

R

R

CLK1

CLK1

OE

Pulling

Capacitors

PD#

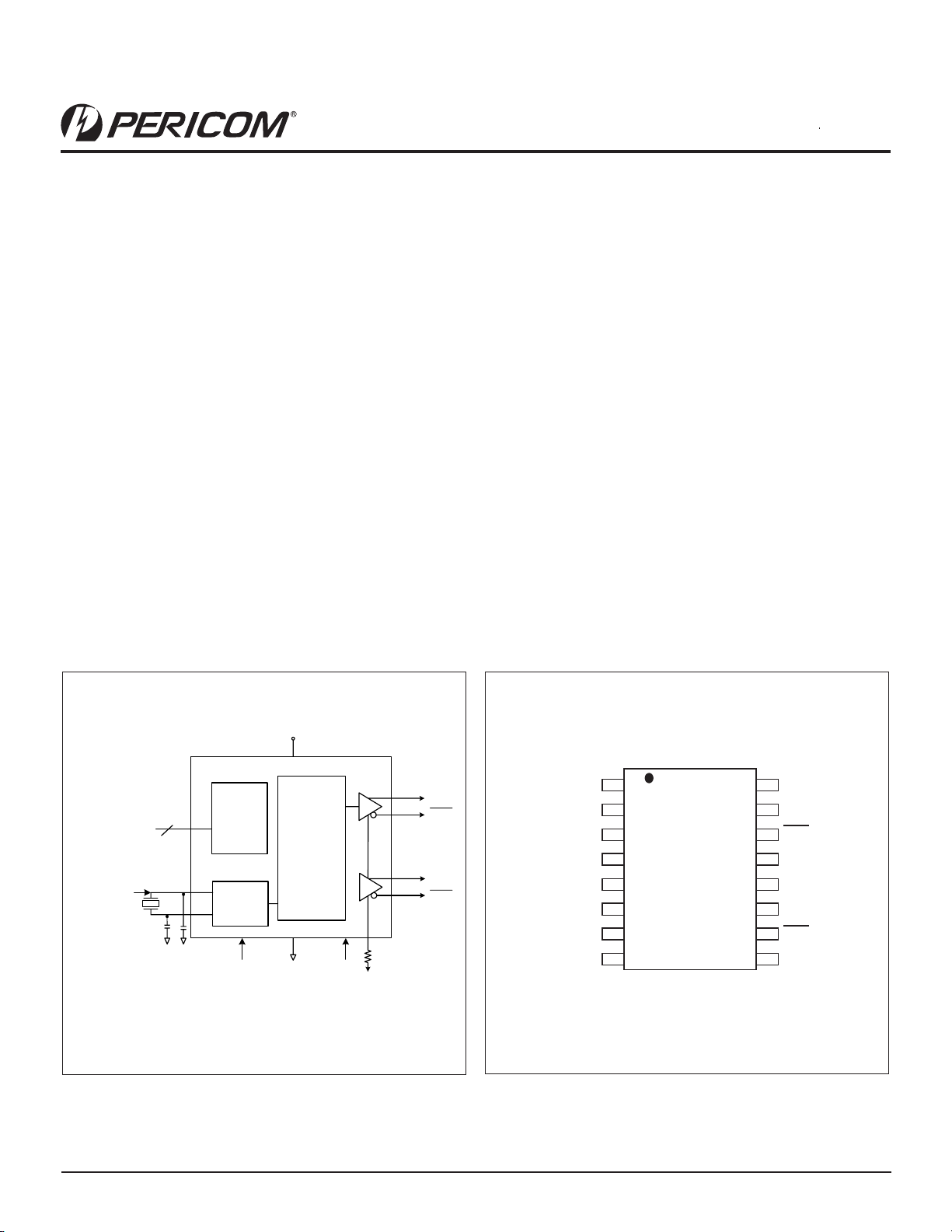

Pin Conguration (16-Pin TSSOP)

S0

S1

PD#

X1/CLK

X2

OE

GND

NC

VDDX

CLK0

CLK0

GNDA

VDDA

CLK1

CLK1

IREF

16

15

14

13

12

11

10

9

1

2

3

4

5

6

7

8

Description

e PI6LC48H02-01 is a clock generator compliant to PCI Ex-

press® 3.0/2.0/1.0 and Ethernet requirements. e device is used

for servers, networking or embedded systems.

e PI6LC48H02-01 provides two dierential (HCSL) or LVDS

outputs. Using Pericom's patented Phase Locked Loop (PLL)

techniques, the device takes a 25MHz crystal input and produces

two pairs of dierential outputs (HCSL) at 25MHz, 100MHz,

125MHz, 200MHz clock frequencies.

Features

PCIe® 3.0/2.0/1.0 compliant

PCIe 3.0 Phase jitter - 0.45ps RMS (High Freq. Typ.)

LVDS compatible outputs

Supply voltage of 3.3V ±10%

25MHz crystal or clock input frequency

HCSL outputs, 0.8V Current mode dierential pair

Jitter 35ps cycle-to-cycle (typ)

RMS phase jitter 12kHz ~ 20MHz @ 100MHz - 0.32ps (typ)

RMS phase jitter 12kHz ~ 20MHz @ 125MHz - 0.3ps (typ)

Power down mode

Industrial temperature range

Packaging: (Pb-free and Green): 16-pin TSSOP (L16)

PCIe® 3.0/2.0/1.0 Clock Generator with 2 HCSL Outputs

15-0125