下载

© 2008 Microchip Technology Inc. DS01120A-page 1

AN1120

INTRODUCTION

This document specifies the theory and operation of

the Ethernet technology found in PIC

®

MCUs with

integrated Ethernet and in stand-alone Ethernet

controllers.

Ethernet technology contains acronyms and terms

defined in Table 1.

APPLICATIONS

Ethernet is an asynchronous Carrier Sense Multiple

Access with Collision Detect (CSMA/CD)

protocol/interface, with a payload size of 46-1500 octets.

With data rates of tens to hundreds of megabits/second,

it is generally not well suited for low-power applications.

However, with ubiquitous deployment, internet

connectivity, high data rates and limitless range

expansibility, Ethernet can accommodate nearly all

wired communications requirements. Potential

applications include:

• Remote sensing and monitoring

• Remote command, control and firmware updating

• Bulk data transfer

• Live streaming audio, video and media

• Public data acquisition (date/time, stock quotes,

news releases, etc.)

THEORY OF OPERATION

Ethernet is a data link and physical layer protocol

defined by the IEEE 802.3™ specification. It comes in

many flavors, defined by maximum bit rate, mode of

transmission and physical transmission medium.

• Maximum Bit Rate (Mbits/s): 10, 100, 1000, etc.

• Mode of Transmission: Broadband, Baseband

• Physical Transmission Medium: Coax, Fiber, UTP, etc.

Author: M. Simmons

Microchip Technology Inc.

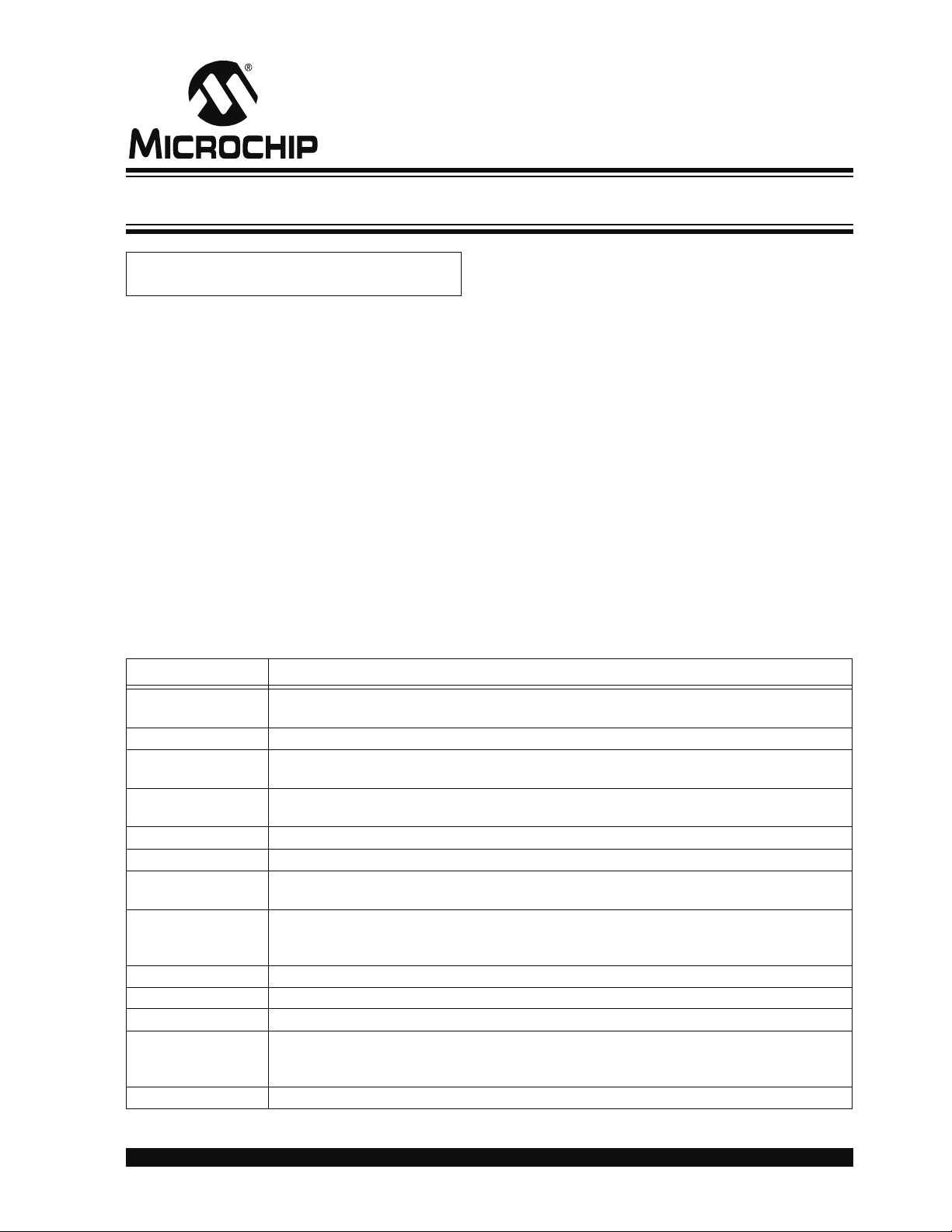

TABLE 1: ETHERNET GLOSSARY

Term Definition

CRC Cyclic Redundancy Check: Type of checksum algorithm used when computing the FCS for all

Ethernet frames and the hash table key for hash table filtering of receive packets.

DA Destination Address: The 6-octet destination address field of an Ethernet frame.

ESD End-of-Stream Delimiter: In 100 Mb/s operation, the ESD is transmitted after the FCS (during

the inter-frame gap) to denote the end of the frame.

FCS Frame Check Sequence: The 4-octet field at the end of an Ethernet frame that holds the error

detection checksum for that frame.

IP Internet Protocol: Refers either to IPv4 or IPv6.

LAN Local Area Network or Large Area Network.

MAC Media Access Control: The block responsible for implementing the Media Access Control

functions of the Ethernet specification.

MAC Address A 6-octet number representing the physical address of the node(s) on an Ethernet network.

Every Ethernet frame contains both a source and destination address, both of which are MAC

addresses.

MDI Medium Dependent Interface or Management Data Input.

MDO Management Data Output.

MDIO Management Data Input/Output.

MII Media Independent Interface: Standard 4-bit interface between the MAC and the PHY for

communicating TX and RX frame data. In 10 Mb/s mode, the MII runs at 2.5 MHz; in

100 Mb/s mode, it runs at 25 MHz.

MIIM MII Management: Set of MII sideband signals used for accessing the PHY registers.

Ethernet Theory of Operation