下载

Maxim > Design Support > Technical Documents > Application Notes > T/E Carrier and Packetized > APP 3894

Keywords: BSDL, JTAG, scan chain, boundary scan, chain mapping

APPLICATION NOTE 3894

DS26522 JTAG Scan Chain Mapping

Sep 05, 2006

Abstract: This application note describes the JTAG hardware boundary scan chain for the DS26522

dual-port, single-chip transceiver. The DS26522 is composed of two dice, and the JTAG functionality is

the same as two separate devices daisy chained together. This application note contains a complete

breakdown of the JTAG scan chain and explains how to access all of the scan cells in the boundary.

Overview

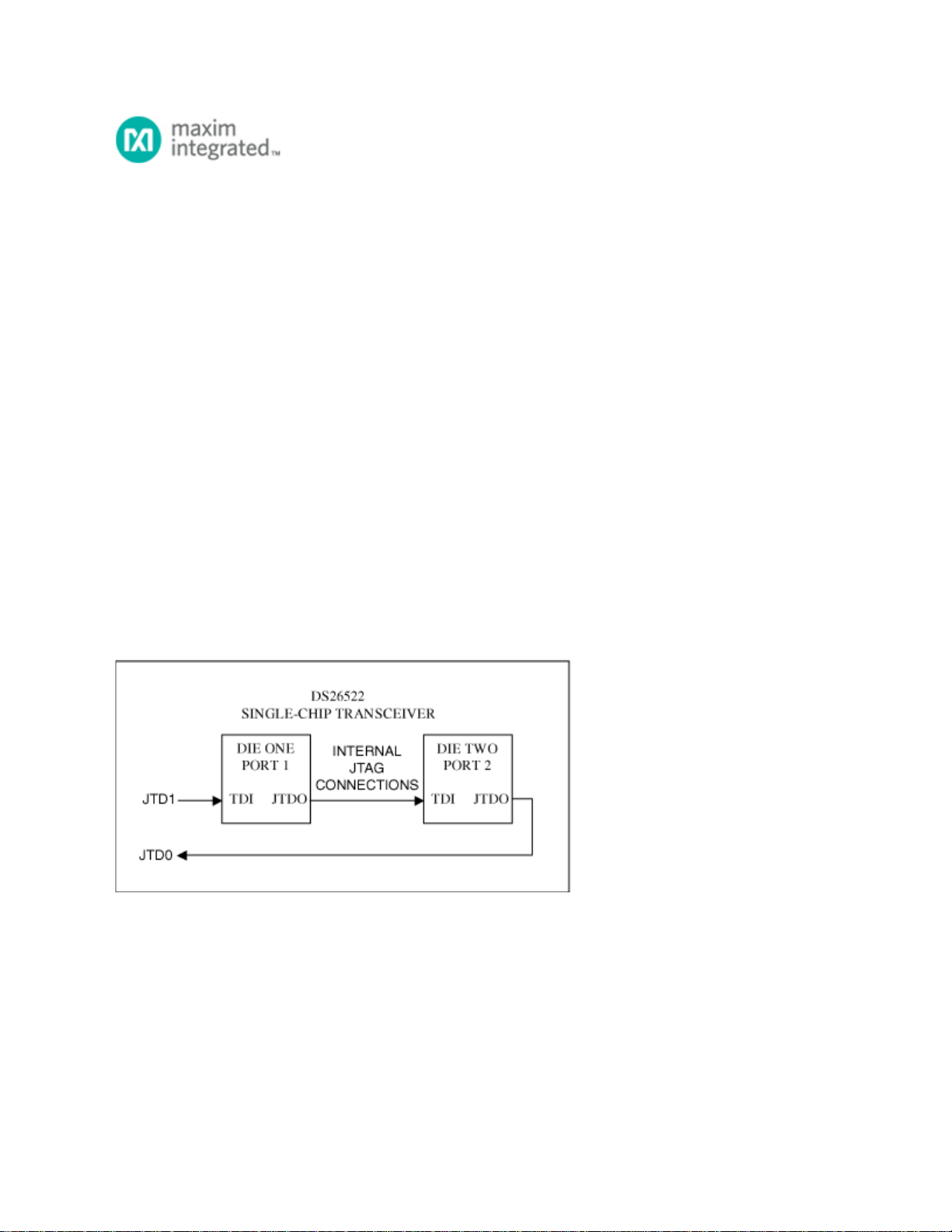

This application note describes the JTAG hardware boundary scan chain for the DS26522 dual-port

T1/E1/J1 single-chip transceiver (SCT). It is a dual-die module with two separate JTAG controllers in the

same package (see Figure 1). Notice the internal JTAG connections. The JTDI pin is connected to the

JTDI input of the first die (port 1), while the JTDO pin is connected to the JTDO output of the second die

(port 2). JTRST, JTCLK, and JTMS are wired together in parallel to both ports. This causes the

DS26522 to appear as two separate devices in any JTAG software application. To solve this issue, two

BSDL files have been created: one for port 1 and one for port 2.

Figure 1. DS26522 JTAG Scan Chain

If the user would like to do any type of JTAG testing that requires a board netlist, the netlist will need to

be modified to ensure that there are two unique instances of the DS26522 that correspond to the two

BSDL files. Table 1 contains the port location (SCT port), the pin names, BSDL cell scan position, BSDL

cell name and other useful information that correspond to the pins in each BSDL file. The table has been

sorted by port location (SCT number) and then BSDL cell scan position. This should allow easy access

to the necessary information about which BSDL cell scan position maps to which port location and BGA

pin number. Incomplete or incorrect JTAG testing can be caused by the failure to modify the netlist

accordingly.

Page 1 of 7