www.ti.com

FEATURES DESCRIPTION

APPLICATIONS

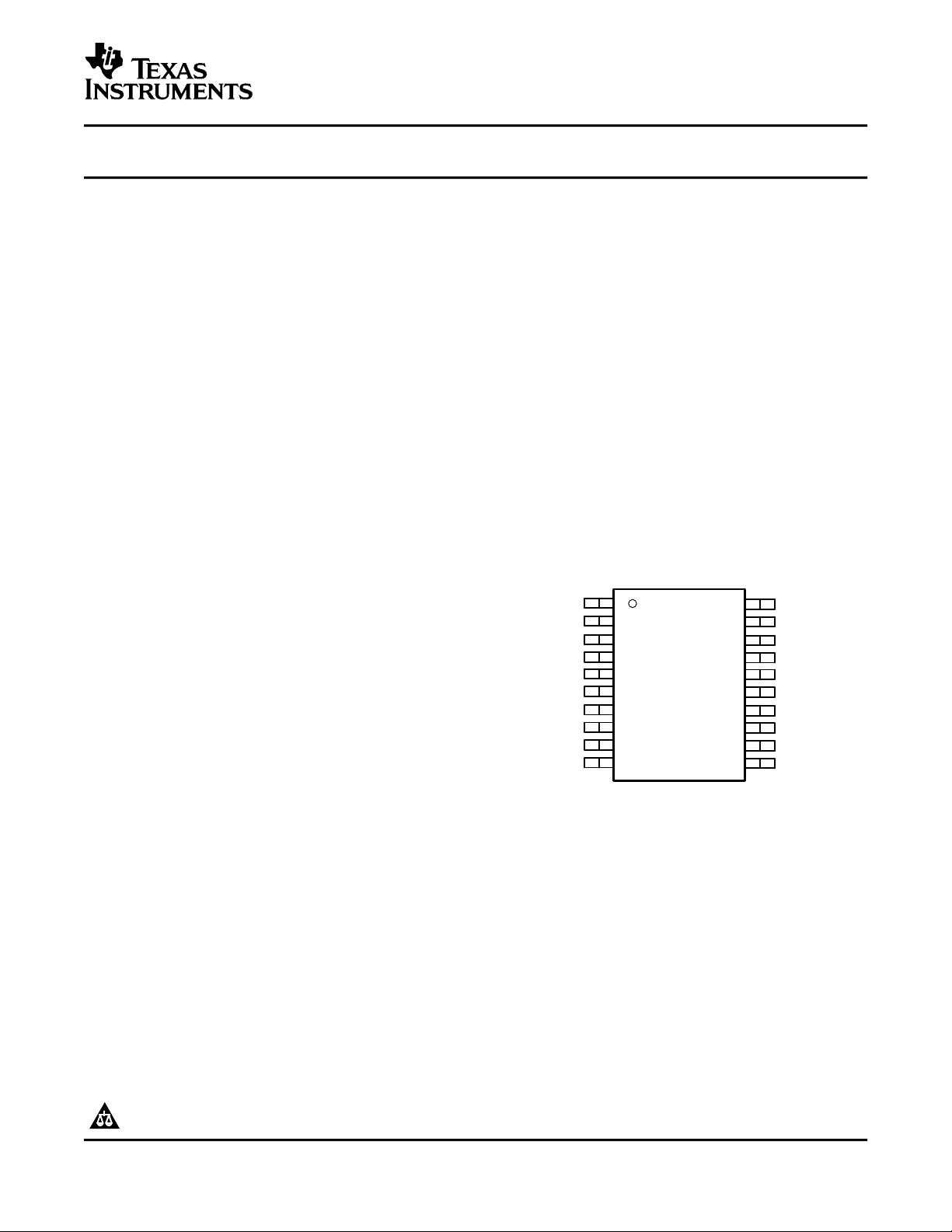

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

VIDSEL

REF_IN

PLL1VDD

VIDCLK

PLL1VSS

PLL2VDD

AUDCLK

PLL2VSS

AUDSEL

MCSEL

ASICCLK

PLL3VDD

PLL3VSS

CPUCLK

PLL3VDD

PLL3VSS

USBCLK

PLL3VDD

PLL3VSS

MCCLK

PW PACKAGE

(TOP VIEW)

CDC5806

SCAS760A – MARCH 2004 – REVISED JULY 2004

THREE PLLs BASED CLOCK GENERATOR FOR DIGITAL TV APPLICATIONS

• High Performance Clock Generator

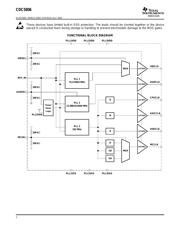

The CDC5806 is a clock generator which synthesizes

video clocks, audio clocks, CPU clock, ASIC clock,

• Clock Input Compatible With LVCMOS/LVTTL

USB clock, and a memory card clock from a 54-MHz

• Requires a 54-MHz Input Clock to Generate

system clock.

Multiple Output Frequencies

Three phase-locked loops (PLLs) are used to

• Low Jitter for Clock Distribution

generate the different frequencies from the system

• Generates the Following Clocks:

clock. On-chip loop filters and internal feedback

– VIDCLK 74.175824 MHz/54 MHz

eliminate the need for external components.

(Buffered)

Since the CDC5806 is based on PLL circuitry, it

– AUDCLK 16.9344 MHz/12.288 MHz

requires a stabilization time to achieve phase-lock of

the PLLs. The PLL stabilization time begins after the

– CPUCLK 64 MHz

reference clock input has a stable phase and

– ASICCLK 32 MHz

frequency.

– USBCLK 48 MHz

The device operates from a single 3.3-V supply

– MCCLK 38.4 MHz/19.2 MHz/12 MHz

voltage. The CDC5806 device is characterized for

• Operates From Single 3.3-V Supply

operation from -40°C to 85°C.

• Low Peak-to-Peak Period Jitter (150 ps

Max)

• PLLs Are Powered Down, if No Valid REF_IN

Clock (< 5 MHz) is Detected or the

V

DD

is Below 2 V

• PLL Loop Filter Components Integrated

• Packaged in TSSOP (PW) 20-Pin Package

• Industrial Temperature Range -40°C to

85°C Applications

• Digital Television With a Memory Card

Interface

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date.

Copyright © 2004, Texas Instruments Incorporated

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.